# Maintaining High Performance in the Presence of Impossible-to-Predict Branches

Stephen Pruett

# High Performance Systems Group Department of Electrical and Computer Engineering The University of Texas at Austin Austin, Texas 78712-0240

TR-HPS-2022-001 May, 2022 Copyright

by

Stephen Pruett

2022

The Dissertation Committee for Stephen Pruett certifies that this is the approved version of the following dissertation:

# Maintaining High Performance in the Presence of Impossible-to-Predict Branches

| Committee:              |  |  |

|-------------------------|--|--|

|                         |  |  |

| Yale Patt, Supervisor   |  |  |

| Mattan Erez             |  |  |

|                         |  |  |

| Mohit Tiwari            |  |  |

| Christopher J. Rossbach |  |  |

| Robert S. Chappell      |  |  |

| HODELLO, CHADDELL       |  |  |

# Maintaining High Performance in the Presence of Impossible-to-Predict Branches

$\mathbf{b}\mathbf{y}$

# Stephen Pruett

# DISSERTATION

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

#### DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT AUSTIN  ${\rm August~2022}$

# Acknowledgments

Completing this dissertation would not have been possible without the love and support of my family, friends, and fellow graduate students. There are so many people that helped me in so many ways throughout this journey and there is simply not enough space to thank everyone. However, I would like to thank a few people here.

First, I thank my mother, Margaret Pruett, without whom I would not be where I am today. My mom always gave me the help and support I needed to succeed academically. She required that I participate in extracurricular activities and supported me as my ever changing interests caused me to bounce from sports to music to film. She enrolled me in programs that helped me build a strong academic foundation, which ultimately helped me become a successful engineer. She also supported me financially, allowing me to choose my path without the burden of financial decisions. Mom, it is not possible to thank you enough for all you have done for me over the years. I know you were hoping that I would one day become a music major. I hope that my Ph.D. in computer engineering will suffice.

I thank my father and step mother, Jeff and Gayla Pruett, for the support they have given me. They have always visited me while I was away on internships and called me to check on how I was doing. In particular, they

are always quick to come up with a plan for getting some much needed rest and relaxation. My dad has taught me so many things over the years, but in particular I think back to all the projects we have worked on together. When I was a kid, the first thing I ever said I wanted to be was a builder. My dad helped me cultivate that talent and creativity, which no doubt played a role in me eventually becoming an engineer. Gayla has always been incredibly supportive and patient, as at least a few of these projects have remained unfinished in her backyard. They have also supported me financially, which helped me pursue my dreams.

I thank my sister and brother-in-law, Lauren and Cyrus Manekshaw. My sister was a roll model while growing up and has always been quick to drop whatever is going in her life to help me when I need her most. I consider myself very lucky that Cyrus found his way into our family. His kindness and sense of humor fit right in, and I of course always appreciate our late night runs to Andy's. I look forward to watching their children, Zubin and Zara, grow up and perhaps one day reading their dissertations.

I thank my grandparents, Tom and Jo Phalen and Jerry and Pat Pruett. I still remember working on my multiplication tables with my Grandpa Phalen, reading books with my Grandma Phalen, playing card games with my Grandma Pruett (somehow I always won!), and working on projects in my Grandpa Pruett's garage. Given that I am the grandchild of two teachers and two engineers, it is no wonder where my passion for both engineering and teaching has come from.

I thank past and present members of HPS, including Aater Suleman, Carlos Villavieja, Jose Joao, Rustam Miftakhutdinov, Milad Hashemi, Faruk Guvenilir, Ben Lin, Siavash Zangeneh, Ali Fakhrzadehgan, Aniket Deshmukh, and Chester Cai. Each of them are always willing to stop what they are working on and help with whatever challenge I may be facing, whether it is related to research or not. They provide an environment of openness, candidness, and support that makes for an ideal research environment. In particular, I would like to thank:

- Aater, for the help and graduate school advise you gave me during my first year as a graduate student. Your ability to brainstorm and break down complex research ideas was an early inspiration for me. Your perspective on how to approach graduate school was something I reflected back on often, and recently your perspective on joining a start up helped me decide what I will do next.

- Carlos, for working with me throughout my senior year of undergrad and

my first year in graduate school. You helped be get started with research

and to eventually become a member of HPS.

- Jose, for your advise and kindness, both early on in my Ph.D. and recently while looking for a job.

- Rustam, for looking over my shoulder during my first year and asking me tough questions about what I was working on. Although you may not

realize it, your inclusiveness during my first year helped me acclimate to graduate school and working with HPS. Your attention to detail and tough questions have improved my research over the years. You have also helped in many situations where you did not need to, including proof reading papers, teaching me how to use Scarab, and dry running my first presentation to Yale. I also thank you for your mentorship during internships and teaching me how to play foosball.

- Milad, for his brutally honest feedback and willingness to tell me when

my research was headed in the wrong direction. Although I did not

always immediately listen, your advise was often correct and eventually

led me in the right direction. I also appreciated your willingness to share

a bottle of North Korean wine with me.

- Faruk, for patiently and painstakingly teaching me interrupts, virtual memory, and a variety of other topics throughout my undergrad as well as many other things over the years. You are one of the best teachers I know, and it is something that has truly been an inspiration to me. I always appreciated discussing research with you, as your natural teaching instincts and desire to deeply understand everything always left me understanding my own research that much better.

- Ben, for the conversations on our walks home after a long night of research. Your openness and friendship helped me fully acclimate and find my place in the research group. You have always been around and

willing to help out with my research, and your help proof reading my papers has been essential. Your good attitude and sense of humor always brightened the office and made our group fun to work in.

- Siavash, for being my partner in all things branch prediction. Your deep understanding on a variety of topics as well as your creativity unlocked a number of interesting research projects that I am extremely proud to be a part of. You have taught me so many things and helped me in so many ways over the years that it is hard to list them out here. I am particularly grateful for our time TAing together, the late nights working on the branch prediction competition together, and all of the interesting topics that I got to research with you. Also for your deep appreciation of Dr. Pepper and Chick-fil-A.

- Ali, for our walks, good discussing, and of course always joining me in the longhorn run. I particularly appreciate the time you spent helping me with my papers and teaching me Farsi.

- Aniket and Chester, for taking up the mantle in HPS. Getting the opportunity to see each of you develop and show off your creativity has been inspiring.

I thank Austin Harris, Taylor Morrow, David Knopf, and Ali Mohandesi for being the best study group anyone could ask for during our undergrad. Our countless late nights and hard work helped me build the strong foundation in computer engineering that I relied on all through out graduate school. Having y'all as partners enabled me to take on so many challenges in undergrad that I am still extremely proud of today. Additionally, I thank Austin for being a fantastic roommate and for having to put up with me slightly more than everyone else, Taylor for your encyclopedic knowledge on all topics as well as your continued friendship, David for bringing us all together, and Ali for making sure we always took time to have fun.

I thank my fellow graduate students, including Jeremie Kim, Zach Myers, and Swamit Tannu for your friendship and guidance throughout graduate school.

I thank my friends Matt Brown, Sam Chacon, Laura Condon, Stafford Hutchins, Adrian Orozco, Corey Rose, Manuel Santiago, Spencer Walker, and Blake Wolf. I appreciate the efforts you all go through to make sure we have continued to stay in touch. Our long and continued friendship is something that I deeply appreciate.

I thank my internship managers, Rob Chappell, Belli Kuttanna, Burton Smith, Doug Carmean, Tom Huff, and Kulin Kothari for giving me great learning opportunities in industry. In particular I would like to thank Rob Chappell for the many conversations and good advice he has given me over the years.

I also thank the ECE administrative staff, in particular Leticia Lira for her outstanding support of our research group, Melanie Gulick for her quick and attentive responses and always making sure I had all the right forms, and Melody Singleton for her hard work and help during ECE visit days.

I thank Mattan Erez, Mohit Tiwari, Chris Rossbach, and Rob Chappell for serving on my dissertation committee and for the valuable feedback that improved this dissertation.

Finally, I thank my advisor, Yale Patt. Like many of his students, my first exposure to Yale was in his EE 306 class, Introduction to Computing. It was this course that started my interest in computer architecture. Additionally, it was Yale's approach to teaching that inspired me to build a strong foundation and never put a ceiling on what I could accomplish. He challenged me to strive for a well rounded education, not just focusing on math and engineering, but also focusing on the importance of good writing and communication skills. Yale sets the bar high, and expects you to measure up. An exercise that can be challenging, but one that I am very grateful for. I am most inspired by his amazing ability to teach and get the most out of his students. That is a quality that I hope I can one day achieve myself.

Stephen Pruett

May 2022, Austin, TX

Maintaining High Performance in the Presence of Impossible-to-Predict Branches

by

Stephen Pruett, Ph.D.

The University of Texas at Austin, 2022

SUPERVISOR: Yale Patt

High performance microprocessors have relied on accurate branch predictors to maintain high instruction supply for over 30 years. Unfortunately, as instruction windows and pipeline widths have continued to grow, misprediction penalties have gotten worse. Branch predictors have failed to improve at a fast enough rate to counteract these penalties. Impossible-to-predict branches, such as data-dependent branches, have become the worst offender since, so far, no viable predictor exists for these branches. I propose to identify such branches at runtime, and replace the inaccurate branch prediction with a more accurate merge point prediction. Doing so enables techniques that can either pre-compute the result of the branch, as is the case for Branch Runahead, or avoid the misprediction altogether by dynamically predicating instructions, or fetching instructions out-of-order; i.e., from the merge point until the branch direction has been determined. This dissertation presents a

new merge point prediction algorithm that achieves a higher accuracy and coverage than prior work, and uses it to enable three mechanisms for dealing with impossible-to-predict branches: Branch Runahead, Dynamic Predication, and Delayed Fetch.

# **Table of Contents**

| Ackno   | wledgments                                            | 5  |

|---------|-------------------------------------------------------|----|

| Abstra  | act                                                   | 12 |

| List of | Tables                                                | 18 |

| List of | Figures                                               | 19 |

| Chapt   | er 1. Introduction                                    | 21 |

| 1.1     | The Problem: The Conditional Branch Bottleneck        | 21 |

| 1.2     | Impossible-to-Predict Branches                        | 23 |

| 1.3     | Detecting Hard-to-Predict Branches                    | 24 |

| 1.4     | Merge Point Prediction                                | 26 |

| 1.5     | Pre-computation: Branch Runahead                      | 26 |

| 1.6     | Control Independence                                  | 27 |

|         | 1.6.1 Dynamic Predication                             | 27 |

|         | 1.6.2 Delayed Fetch                                   | 28 |

|         | 1.6.3 Combining Dynamic Predication and Delayed Fetch | 29 |

| 1.7     | Thesis Statement                                      | 30 |

| 1.8     | Contributions                                         | 30 |

| 1.9     | Dissertation Organization                             | 31 |

| Chapt   | er 2. Hard-to-Predict Branch Detection                | 32 |

| 2.1     | Introduction                                          | 32 |

| 2.2     | Limitations of Prior Work                             | 33 |

| 2.3     | Detecting Branches with High Misprediction Rates      | 34 |

|         | 2.3.1 The Arithmetic Model                            | 35 |

|         | 2.3.2 Hard Branch Table                               | 38 |

| 2.4     | Branch Cost                                           | 38 |

| 2.5   | Detecting Branches with High Branch Cost                   | 40 |  |  |

|-------|------------------------------------------------------------|----|--|--|

|       | 2.5.1 Branch Cost Table                                    | 41 |  |  |

| 2.6   | Related Work                                               | 41 |  |  |

| 2.7   | Future Work                                                | 42 |  |  |

| Chapt | er 3. Merge Point Prediction                               | 44 |  |  |

| 3.1   | Introduction                                               |    |  |  |

| 3.2   | Motivation                                                 | 45 |  |  |

|       | 3.2.1 Weaknesses of Detecting Merge Points at Compile Time | 46 |  |  |

|       | 3.2.2 Weaknesses of Prior Work in Merge Point Prediction   | 48 |  |  |

| 3.3   | Dynamic Merge Point Prediction                             | 49 |  |  |

|       | 3.3.1 Merge Predictor Design                               | 50 |  |  |

|       | 3.3.1.1 Detecting New Merge Points                         | 52 |  |  |

|       | 3.3.1.2 Design of the WPB                                  | 54 |  |  |

|       | 3.3.1.3 Making the Prediction                              | 55 |  |  |

|       | 3.3.1.4 Updating the Predictor                             | 56 |  |  |

| 3.4   | Evaluation Methodology                                     |    |  |  |

| 3.5   | Results and Analysis                                       | 59 |  |  |

| 3.6   | Prior Work                                                 | 62 |  |  |

| 3.7   | Future Work                                                | 64 |  |  |

| Chapt | er 4. Branch Runahead                                      | 66 |  |  |

| 4.1   | Introduction                                               | 66 |  |  |

| 4.2   | Limitations of Prior Work                                  | 71 |  |  |

|       | 4.2.1 Limitations of Compiler-based Techniques             | 71 |  |  |

|       | 4.2.2 Limitations of Prior Runtime Techniques              | 73 |  |  |

|       | 4.2.3 Limitations of Heavy-weight Helper Threads           | 74 |  |  |

| 4.3   | Motivational Example                                       | 76 |  |  |

| 4.4   | Branch Runahead Microarchitecture                          |    |  |  |

|       | 4.4.1 Dependence Chain Control                             | 81 |  |  |

|       | 4.4.2 DCE Microarchitecture                                | 84 |  |  |

|       | 4.4.3 Chain Extraction Hardware                            | 89 |  |  |

|       | 4.4.4 Detecting Affector and Guard Branches                | 93 |  |  |

| 4.5 Results      |        | ts                                                             | 95  |

|------------------|--------|----------------------------------------------------------------|-----|

|                  | 4.5.1  | Evaluation Methodology                                         | 95  |

|                  | 4.5.2  | Branch Runahead Results                                        | 97  |

| 4.6 Related Work |        |                                                                | 106 |

| 4.7              |        |                                                                |     |

| Chapt            | er 5.  | Control Independence                                           | 110 |

| 5.1              | Intro  | duction                                                        | 110 |

|                  | 5.1.1  | Dynamic Predication                                            | 111 |

|                  | 5.1.2  | Delayed Fetch                                                  | 112 |

|                  | 5.1.3  | The Duality of Dynamic Predication and Delayed Fetch.          | 113 |

| 5.2              | Limit  | ations of Prior Work                                           | 115 |

|                  | 5.2.1  | Limitations of Compiler Predication                            | 115 |

|                  | 5.2.2  | Dynamic Predication                                            | 116 |

|                  | 5.2.3  | Delayed Fetch                                                  | 117 |

| 5.3              | Critic | eal Issues                                                     | 119 |

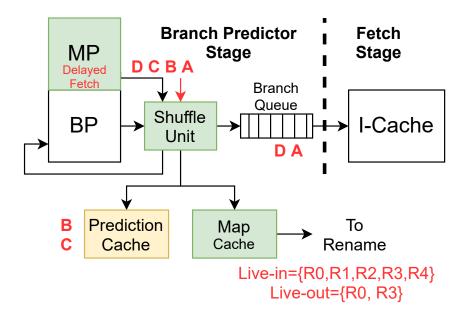

|                  | 5.3.1  | Branch Prediction and Instruction Fetch                        | 120 |

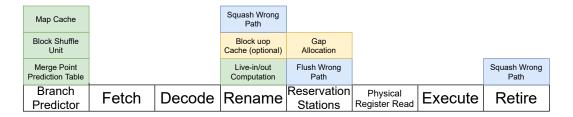

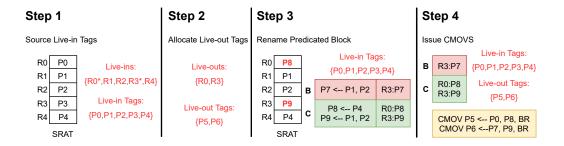

|                  | 5.3.2  | Rename                                                         | 127 |

|                  | 5.3.3  | Gap Allocation, Deadlock, and Full Window Stalls $\ . \ . \ .$ | 129 |

| 5.4              | Contr  | rol Independent Microarchitecture                              | 130 |

|                  | 5.4.1  | Merge Point Prediction                                         | 130 |

|                  | 5.4.2  | Changes to the Branch Predictor Stage                          | 135 |

|                  | 5.4.3  | Changes to Rename                                              | 138 |

|                  | 5.4.4  | Squashing wrong-path instructions                              | 140 |

|                  | 5.4.5  | Out-of-order Rename                                            | 140 |

|                  | 5.4.6  | Gap Allocation and Tracking                                    | 141 |

|                  | 5.4.7  | Waste-based Throttling                                         | 142 |

| 5.5              | Resul  | ts                                                             | 144 |

|                  | 5.5.1  | Evaluation Methodology                                         | 144 |

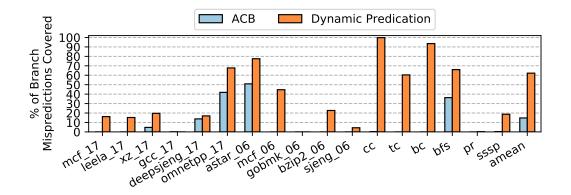

|                  | 5.5.2  | Coverage Results                                               | 146 |

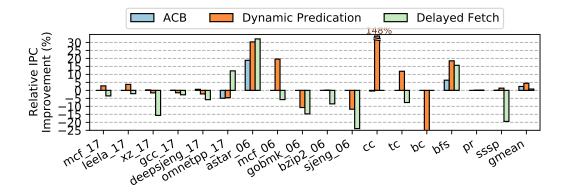

|                  | 5.5.3  | Performance Results                                            | 147 |

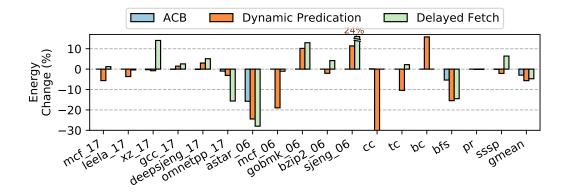

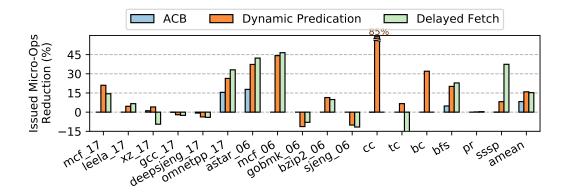

|                  | 5.5.4  | Energy Results                                                 | 151 |

| Bibliog | graphy | 7                              | 161 |

|---------|--------|--------------------------------|-----|

| Chapte  | er 6.  | Conclusion                     | 158 |

|         | 5.7.4  | Specialized Loop Predictor     | 156 |

|         | 5.7.3  | Utilizing TAGE confidence      | 155 |

|         | 5.7.2  | Critical Path Based Throttling | 154 |

|         | 5.7.1  | Eliminating MOV micro-ops      | 154 |

| 5.7     | Future | e Work                         | 154 |

| 5.6     | Relate | ed Work                        | 153 |

# List of Tables

| 2.1 | Definition of variables for the Arithmetic Model        | 35  |

|-----|---------------------------------------------------------|-----|

| 3.1 | System Configuration                                    | 58  |

|     | Baseline Configuration                                  |     |

| 5.1 | Reciprocal trade-offs of control-independent strategies | 113 |

| 5.2 | Merge Point Predictor Structures                        | 131 |

| 5.3 | Baseline Configuration                                  | 143 |

# List of Figures

| 1.1  | Percentage of processor cycles wasted due to fetching wrong-<br>path instructions. Table 4.1 contains the system configuration. |     |  |

|------|---------------------------------------------------------------------------------------------------------------------------------|-----|--|

| 3.1  | Example Control Flow Graph (CFG)                                                                                                | 45  |  |

| 3.2  | All three newly added structures: Merge Predictor Table, Update List and WPB.                                                   |     |  |

| 3.3  | Wrong-path instructions copied from the ROB to the WPB                                                                          | 53  |  |

| 3.4  | Interaction between the Branch Predictor (BP), Branch Target Buffer (BTB), and Merge Predictor (MP)                             |     |  |

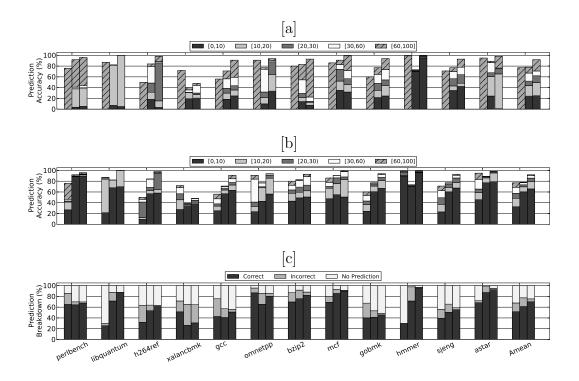

| 3.5  | Final Merge Point Predictor Results                                                                                             | 60  |  |

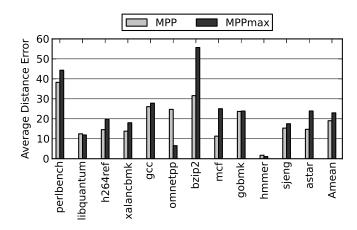

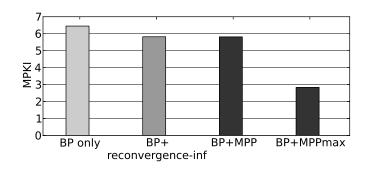

| 3.6  | Average difference between predicted and true distances                                                                         | 61  |  |

| 3.7  | Projected MPKI with Merge Point Prediction                                                                                      | 63  |  |

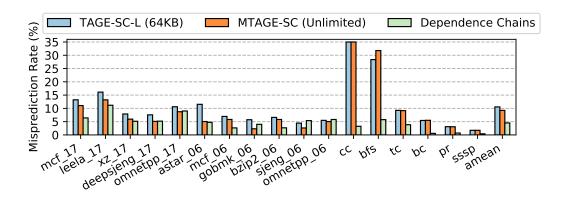

| 4.1  | Misprediction Rate: TAGE-SC-L (64KB) vs MTAGE-SC (Unlimited) vs Dependence Chains for Hard-to-Predict Branches .                | 67  |  |

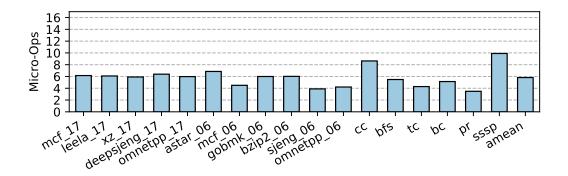

| 4.2  | Average Length of Dependence Chains                                                                                             | 69  |  |

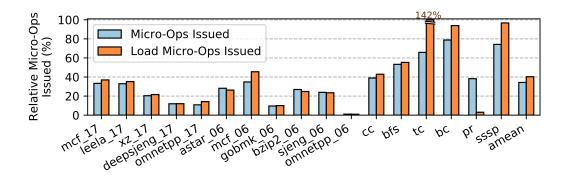

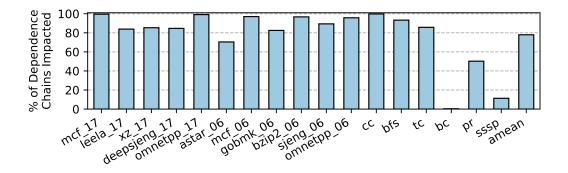

| 4.3  | Increase in micro-ops due to Branch Runahead                                                                                    | 72  |  |

| 4.4  | Code snippet from leela, a SPEC 2017 benchmark [3]                                                                              | 75  |  |

| 4.5  | Dependence Chains with Affectors or Guards                                                                                      | 77  |  |

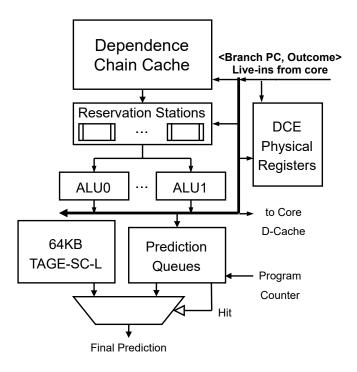

| 4.6  | Pipeline Modifications                                                                                                          | 80  |  |

| 4.7  | DCE Microarchitecture                                                                                                           | 84  |  |

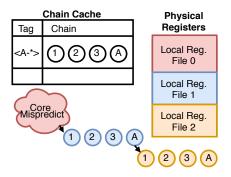

| 4.8  | Global Rename Example                                                                                                           | 87  |  |

| 4.9  | The Chain Extraction Buffer (CEB)                                                                                               | 89  |  |

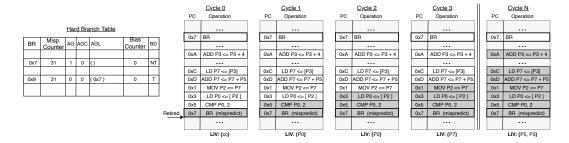

| 4.10 | , ,                                                                                                                             |     |  |

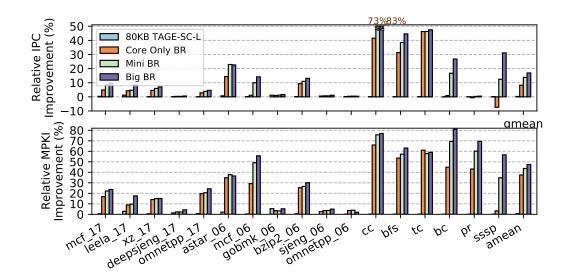

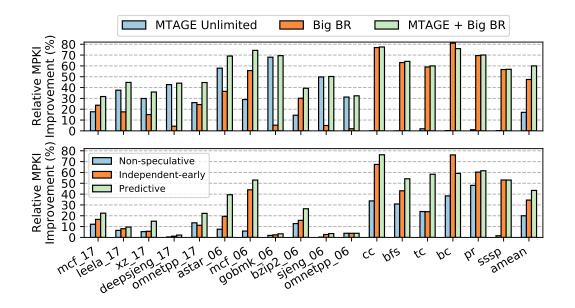

| 4.11 | MPKI Improvement of MTAGE and Branch Runahead (top) and MPKI Improvement of Chain Initiation Methods (bottom)                   | 99  |  |

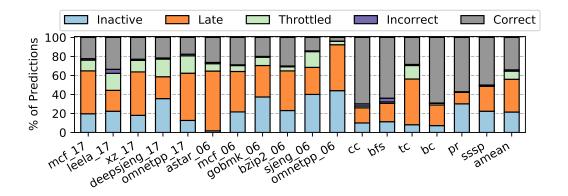

| 4.12 | Prediction Breakdown                                                                                                            | 100 |  |

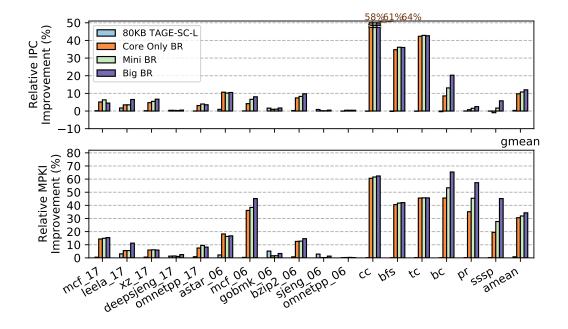

| 4.13 | IPC and MPKI Improvement of Branch Runahead on a 16-wide fetch, 1024-entry instruction window baseline                          | 101 |  |

|      |                                                                                                                                 |     |  |

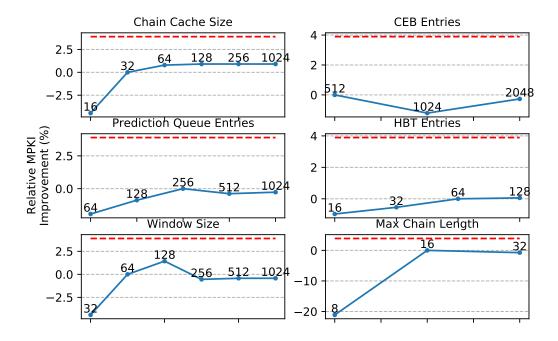

| 4.14 | MPKI Improvement relative to Mini Branch Runahead. Parameters are swept individually up to the level of Big Branch Runahead (Red dotted line) to show each parameters contribution | 104 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.15 | Energy Impact (Lower is better)                                                                                                                                                    | 105 |

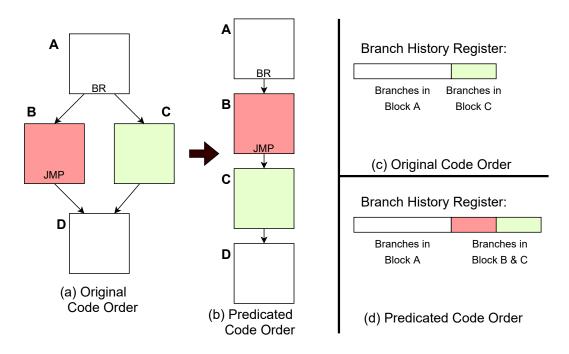

| 5.1  | Original Code Order (left) and Predicated Code Order (right). Red indicates wrong-path instructions, green is correct-path.                                                        | 121 |

| 5.2  | Changes to the pipeline. Blue indicates logic required for Dynamic Predication, yellow indicates logic needed for Delayed Fetch, and green indicates logic needed for both         | 130 |

| 5.3  | Merge Point Predictor                                                                                                                                                              | 132 |

| 5.4  | Changes to the Branch Predictor Stage. The red text is an example highlighting the difference between branch prediction order and fetch order                                      | 136 |

| 5.5  | Fast Path Rename                                                                                                                                                                   | 138 |

| 5.6  | Percentage of Branch Misprediction covered by the ACB vs our merge point predictor                                                                                                 | 146 |

| 5.7  | IPC Improvement of ACB, Dynamic Predication, and Delayed Fetch without throttling techniques                                                                                       | 147 |

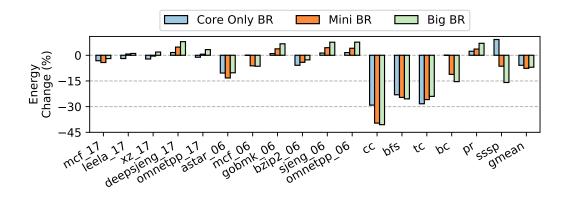

| 5.8  | Change in Energy for Dynamic Predication and Delayed Fetch.                                                                                                                        | 151 |

| 5.9  | Reduction in total micro-ops issued to the execution units for Dynamic Predication and Delayed Fetch                                                                               | 152 |

# Chapter 1

# Introduction

# 1.1 The Problem: The Conditional Branch Bottleneck

High performance microprocessors require high levels of instruction supply. As instruction windows and fetch rates continue to grow, the demand for higher levels of instruction supply rises. Continued improvements in branch prediction accuracy have been the most important driver of this for nearly 30 years. Unfortunately, modern predictors are increasingly bottlenecked by hard-to-predict branches. While branch prediction accuracy will continue to improve in the future, the rate of improvement is being outpaced by the demand for increased instruction supply. Unfortunately, there are many branches, such as data-dependent branches, that are impossible for traditional history-based predictors to predict accurately. In these cases, branch prediction will always fall short. Despite this, branch prediction remains the only runtime solution for conditional branches.

Existing microarchitectures must predict all conditional branches, even ones on which they have performed poorly in the past. This leads to high branch misprediction rates in the presence of branches that are fundamentally hard-to-predict. Each misprediction corresponds to an expensive pipeline flush

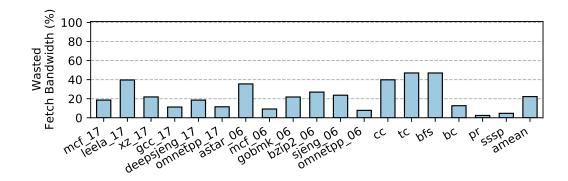

Figure 1.1: Percentage of processor cycles wasted due to fetching wrong-path instructions. Table 4.1 contains the system configuration.

that lowers the effective fetch rate and wastes energy. Figure 1.1 shows the percentage of processor cycles wasted due to fetching wrong-path instructions as a result of branch mispredictions. Each of these cycles, at a minimum, corresponds to wasted power and energy, and often also results in significant performance loss. This all-in approach on branch prediction is particularly problematic when faced with branches that are impossible-to-predict. In these cases, the processor has no ability to dynamically move from branch prediction to alternative methods that may provide higher performance or greater energy efficiency.

Alternatives to branch prediction, such as pre-computation and controlindependence, have been proposed; however, these techniques have limitations, such as heavy dependence on a compiler or high hardware costs that discourage implementation. This dissertation presents a holistic new approach to branch prediction alternatives. To do this, I improve upon essential structures required by branch prediction alternatives, such as hard-to-predict branch detection and merge point prediction. Once the hard-to-predict branches and their merge points have been identified, I use either pre-computation (Branch Runahead) or control independence (Dynamic Predication and Delayed Fetch) to avoid branch prediction altogether.

# 1.2 Impossible-to-Predict Branches

Impossible-to-predict branches are branches for which there is currently no viable predictor that can predict the branch accurately. I.e., the branches are *impossible* on a deep algorithmic level for a given branch predictor, beyond just predicting the bias of the branch. An example of this is data-dependent branches for the TAGE-SC-L predictor [52]. The TAGE predictor offers no ability to specifically target this class of branches beyond predicting the bias of the branch. Therefore, these branches often perform poorly on the TAGE branch predictor. In such cases, simply making the predictor larger will not improve accuracy because the predictor itself is not capable of learning useful information about the branches. The fact that the branch predictor has no ability to learn to predict these branches accurately motivates the branch prediction alternatives presented in this dissertation.

Detecting branches that are truly impossible-to-predict, however, is impractical. Instead, this dissertation detects *hard-to-predict branches*; i.e., branches that TAGE-SC-L performs poorly on. This is done by adding a new structure, the Hard Branch Table (HBT). A branch is contained in the HBT if

its misprediction rate is higher than a given threshold. If a branch hits in the HBT, this means that the branch predictor (for whatever reason) is not able to predict the branch accurately and a branch prediction alternative, such as Branch Runahead, Dynamic Predication, or Delayed Fetch, should be used in its place. If a branch misses in the HBT, it is assumed that the branch is being predicted accurately and the branch will continue to use the branch predictor.

# 1.3 Detecting Hard-to-Predict Branches

The branch prediction alternatives proposed in this dissertation should only be used in cases where the traditional branch predictor fails to achieve high accuracy. Therefore, the first step this dissertation takes is to identify branches for which the branch predictor is performing poorly. The first method discussed detects branches whose misprediction rate exceeds a target threshold. However, as will be shown in this dissertation, not all branch mispredictions are created equal. Long latency branch mispredictions can have a higher impact on performance. In extreme cases, branches that mispredict relatively infrequently can still become bottlenecks if their result depends on a long latency operation, such as a cache miss. To handle these cases, we augment our methodology to also account for branch latency.

Prior work in branch confidence estimation can be categorized as having at least one of the two following issues. First, many prior techniques are *path-based* confidence techniques [51, 19, 4, 36, 20]. The goal of these techniques is to identify the path, or the specific dynamic instance of a branch that is

likely to mispredict. These techniques are really intended to identify specific branch predictions that have low-confidence and throttle only those instances. The techniques presented in this dissertation, however, work on a per-branch basis. These techniques require expensive transformations that are only worth it for branches that contribute many mispredictions throughout the entire program. Second, many prior techniques are too dependent on recent branch behavior [26, 51, 55, 19]. For example, the JRS confidence predictor [26] resets its confidence counter on each misprediction, classifying a branch as low confidence if it has mispredicted recently. The techniques presented in this dissertation benefit more from a more stable view of the hard-to-predict branches. Ideally, we would like to generate a list of the top N hard-to-predict branches in the workload and only update that list if another branch proves to be in that top N.

To address these shortcomings, I introduce the Hard Branch Table (HBT). The HBT is a small table that monitors the retired instructions stream for branch mispredictions. The table uses a Leaky Bucket counter [24] to detect branches whose misprediction rate exceeds a given threshold. An arithmetic model is used to compute the parameters of the HBT based on the target misprediction rate and an acceptable false positive rate. Furthermore, Chapter 2 discusses how to extend the HBT to account for branch waste; i.e., the impact each branch misprediction has on performance. With this, the HBT is used to detect which branches will benefit the most from Branch Runahead, Dynamic Predication, and Delayed Fetch.

# 1.4 Merge Point Prediction

An important contribution of this dissertation which is necessary for the alternatives to branch prediction is a much more accurate merge point predictor than anything available prior to this dissertation. Prior approaches use compiler heuristics and assumptions about code layout to predict the location of the merge point that do not reliably locate the best merge point. My work takes advantage of branch mispredictions by comparing instructions fetched from both the wrong path and the correct path to detect the merge point. This approach is more accurate and reliable than prior work.

The merge point predictor is able to achieve an average accuracy of 95% across the SPEC CPU2006 benchmark suite [3]. The improved accuracy results in successfully detecting and replacing 58% of all branch mispredictions with a correct merge point prediction, reducing the MPKI by an average of 43%. This dramatic improvement in coverage gives us more opportunity to substitute an alternative for branch prediction in cases where the branch predictor performs poorly.

# 1.5 Pre-computation: Branch Runahead

Branch Runahead is a mechanism that uses lightweight dependence chains to pre-compute the result of hard-to-predict, data-dependent branches. Prior work used the compiler to create a filtered version of the original program, only containing instructions necessary to compute the result of hard-topredict branches. The filtered thread, or "helper" thread, is executed asynchronously on another core [59, 31], on another Simultaneous Multi-threading (SMT) context [64, 49, 11, 10], or on a dedicated unit within the core [54]. These approaches are fundamentally more costly as they require use of the compiler and/or re-executing most instructions (85%) in the program, and thereby require expensive resources to pre-compute the branch.

Dependence chains are far simpler than the helper threads proposed by prior work, which allows them to be accelerated on a small, simple hardware structure, rather than another core or SMT context. Branch Runahead focuses on predicting hard-to-predict branches; E.g., branches on which TAGE-SC-L [52] performs poorly. In particular, Branch Runahead is ideal for data-dependent branches that have a small number of instructions required to compute the predicate. Branch Runahead, when configured under reasonable hardware constraints, reduces branch MPKI by 47.5% and increases IPC by an average of 16.9%.

# 1.6 Control Independence

#### 1.6.1 Dynamic Predication

Dynamic predication is a runtime mechanism for fetching both paths of a branch, up to the merge point, then executing each path and only committing the results of the correct path. Predication avoids the costly misprediction penalty while also guaranteeing that the correct path is always fetched, decoded, renamed, and executed, even if the branch in question has not completed execution. Once the result of the branch is known, the correct

path results are passed on to any dependent, waiting, post-merge point instructions. In cases where branch mispredictions are frequent, this model can minimize the length of the critical path, as both paths are always executed.

Unfortunately, the wrong path is also always fetched, decoded, renamed, and executed. In some cases, the wasted fetch and execute bandwidth from the wrong path is too great, causing performance inversions; i.e., cases where the performance of branch prediction exceeds that of dynamic predication. Furthermore, predication adds new data dependencies to the data-flow graph, which can increase the length of the critical path and worsen performance.

Prior Dynamic Predication techniques require expensive hardware to track the micro-architectural state of correct-path and wrong-path instructions separately [28]. Other approaches sacrifice early execution of predicated instruction to simplify these hardware demands [12]. My approach to Dynamic Predication will focus on low-cost hardware while still allowing predicated instructions to execute early.

#### 1.6.2 Delayed Fetch

Delayed Fetch is a runtime mechanism that does not fetch instructions from either path of the branch. Instead, Delayed Fetch fetches instructions out-of-order from beyond the merge point. Once the branch has executed and the correct path of the branch is known, Delayed Fetch fetches the correct path of the branch and inserts the delayed instructions into the instruction

window in their correct program order.

The primary benefit of Delayed Fetch is conserving instruction fetch bandwidth since only correct path instructions are fetched. This, however, comes at the expense of correct path latency since correct path instructions are not fetched until the result of the branch is known. This increase in correct path latency can also lead to performance inversions.

Prior approaches only address Delayed Fetch for simple if-then branches [13]. Furthermore, prior work does not address predicting branches out of order, which limits the technique to skipped regions that either do not contain any branches or only contain biased branches. My approach to Delayed Fetch introduces a new technique for handling the branch predictions in the skipped region. This not only enables Delayed Fetch to be used in more cases, but also simplifies other issues like out-of-order Rename.

# 1.6.3 Combining Dynamic Predication and Delayed Fetch

Ultimately, Dynamic Predication reduces the latency of correct path instruction at the expense of fetch, decode, and execute bandwidth, while Delayed Fetch maximizes fetch, decode, and execute bandwidth at the cost of correct path instruction latency. While neither Dynamic Predication nor Delayed Fetch are perfect solutions on their own, the reciprocal nature of their trade-offs make them perfect complements of one another. This dissertation explores combining Dynamic Predication and Delayed Fetch. As such, we propose a single microarchitecture that efficiently implements both techniques.

Further, we demonstrate switching between the techniques on a per application basis. This allows the technique that is most suited towards the needs of the application to be selected. Finally, techniques to switch on a per-branch basis are discussed in the future work section of the chapter.

#### 1.7 Thesis Statement

Dynamic merge point prediction enables effective branch prediction alternatives for impossible-to-predict branches allowing the architecture to dynamically choose between pre-computation or control-independence, thereby avoiding branch mispredictions, resulting in increased performance and energy efficiency.

## 1.8 Contributions

The contributions of this dissertation are as follows:

- A new method for detecting hard-to-predict branches. This dissertation

presents an arithmetic model that can be used to detect branches that

mispredict above a given frequency.

- Further, this model is extended to detect branches that have high cost (i.e., flush a large number of instructions), which is more directly related to performance than misprediction rate alone.

- A new merge point prediction algorithm, which improves both accuracy and coverage over prior work.

- Branch Runahead, a new light-weight pre-computation technique that

generates near perfect branch predictions for data-dependent branches. Branch Runahead improves on prior work by lowering the dynamic instruction footprint of the pre-computation, resulting in a lower hardware and energy overhead.

• A holistic new approach to Dynamic Predication and Delayed Fetch.

This dissertation presents a unified micro-architecture that solves critical issues related to both Dynamic Predication and Delayed Fetch. Further, we present an analysis of both positive and negative results to discuss what areas of control independence need further improvement.

# 1.9 Dissertation Organization

This dissertation is organized into six chapters. Chapter 2 discusses hard-to-predict branch detection. The chapter also defines branch cost, explains why it is more closely related to performance than mispredictions alone, and expands hard branch detection to include branch cost. Chapter 3 discusses the merge point prediction. This includes merge point detection, prediction, and predictor update. Chapter 4 discusses Branch Runahead, a light-weight pre-computation technique for Branch Prediction. The chapter also shows how the merge point predictor can be extended for affector and guard branch detection- a technique that Branch Runahead uses to identify control and data dependencies between branch instructions. Chapter 5 discusses Dynamic Predication and Delayed Fetch, as well as a new holistic micro-architecture that solves critical issues with both. Chapter 6 provides concluding remarks.

# Chapter 2

# Hard-to-Predict Branch Detection

# 2.1 Introduction

This dissertation presents three branch prediction alternatives, Branch Runahead, Dynamic Predication, and Delayed Fetch, that are used when a branch is deemed too hard for the on chip branch predictor to predict. The hard-to-predict branches go through an expensive chain extraction (in the case of Branch Runahead) or code transformation (in the case of Dynamic Predication and Delayed Fetch) process in order to use these techniques. In the case of Branch Runahead, only a limited number of branches (16 branches) can use the pre-computation resources. For these reasons it is important to be selective and decisive when choosing branches for these optimizations. Prior work in branch confidence estimation does not produce stable enough results. Furthermore, prior work is not able to account for the total cost of a branch misprediction. This chapter introduces the Hard Branch Table (HBT)<sup>1</sup>, a new structure that detects branches that mispredict at or above a given threshold. In this chapter, the design of the Hard Branch Table is discussed, as well as the arithmetic model that is used to configure the table. Finally, the chapter

<sup>&</sup>lt;sup>1</sup>A version of the HBT was first introduced in the Branch Runahead [45] paper, which is my own work.

is concluded by discussing Branch Cost, a new metric that tracks the true impact of each branch misprediction on overall performance, and the extensions required to track Branch Cost in the HBT.

### 2.2 Limitations of Prior Work

Jacobsen et al. introduced several confidence mechanisms [26]. Most notably was their confidence mechanism using a simple PC-indexed table of 3-bit counters. The counters are incremented on a correct prediction, and reset on a misprediction. Due to the aggressiveness of resetting the counter on a misprediction, a saturated counter implies a very high degree of confidence. Unfortunately, the counter values can also be unstable, because one misprediction can reset a long history of correct predictions. Further, the counters are very susceptible to phase behavior, meaning that if a branch changes phase, the counters will be reset and confidence must once again be earned. The Hard Branch Table, on the other hand, assumes that some mispredictions occur. In fact, the table is designed in such a way that it can tolerate mispredictions as long as they remain below the target rate. This keeps the classification of hard branches very stable throughout the program. If a branch truly changes phase, turning into an easy branch, it must demonstrate that behavior across multiple periods. This behavior is desirable, as branch prediction alternatives often require a warm up cost before activating. Therefore, stable behavior is preferred.

Seznec proposed a storage-free method for estimating confidence of pre-

dictions from the TAGE branch predictor [51]. While this method is undoubtedly effective and low overhead, it is tied specifically to the TAGE branch predictor. Moreover, this method associates a level of confidence with a particular prediction, rather than generating a cumulative per branch confidence. Currently, all branch prediction alternatives are either activated or deactivated on a per-branch basis. Meaning that, in the context of this dissertation, getting a per-prediction confidence is not useful. In future work, I believe it would be possible to combine the Hard Branch Table together with the Seznec's storage free method to more selectively apply Dynamic Predication and Delayed Fetch techniques (discussed later in this dissertation).

# 2.3 Detecting Branches with High Misprediction Rates

The simplest way to find hard-to-predict branches is by looking at the misprediction rate of retiring branch instructions. We look at misprediction rate (i.e., mispredictions per kilo-instruction) rather than misprediction ratio (i.e., the percentage of the time that a given branch mispredicts) because ultimately we care about minimizing the number of pipeline flushes per kilo-instruction, and misprediction rate directly corresponds to the flush rate.

There are two ways to define hard-to-predict branches. The first is to say that the hard-to-predict branches of a program are the N branches with the highest misprediction rates. This methodology, however, would classify branches as hard-to-predict even if they did not cause very many pipeline flushes, simply because they happened to be in the top N hard to predict

| Variable                              | Definition                                     |

|---------------------------------------|------------------------------------------------|

| Period (D)                            | Length of a period, measured in retired        |

|                                       | branch mispredictions.                         |

| Acceptable Misprediction Rate (AMR)   | An arbitrary threshold where any branch        |

|                                       | mispredicting above threshold is considered    |

|                                       | hard-to-predict.                               |

| Probability of a False Positive (PFP) | An acceptable probability of a false positive; |

|                                       | i.e., the probability that a counter saturates |

|                                       | for a branch that is not hard-to-predict.      |

| p                                     | The probability of a misprediction.            |

Table 2.1: Definition of variables for the Arithmetic Model.

branches in the workload.

Instead we classify hard-to-predict branches based on whether they are above or below a given misprediction rate threshold. The idea being that for every pipeline of a given width and depth there is some level of acceptable flushes per kilo-instruction. As long as the MPKI stays at or below the rate of acceptable flushes, then we do not have a performance/energy problem.

Therefore the goal of the Hard Branch Table is to detect branches that rise above this acceptable rate. Any branch above this threshold may cause problems for performance.

## 2.3.1 The Arithmetic Model

To achieve this, I developed a simple arithmetic model to describe hard branch behavior. I then design a table, the Hard Branch Table, that detects hard branches based on the arithmetic model.

To start, lets consider each static branch individually. The goal is to

determine if a given static branch has a misprediction rate higher than the given acceptable misprediction rate (AMR). To achieve this, I divide time into periods. To keep the math simple, I choose to measure time in retired mispredicted branches.<sup>2</sup> In the general case, the length of the period is D, but an example value of D used throughout this dissertation is D=1000 retired mispredicted branches.

Dividing time into periods allows us to break up the problem into two pieces: 1) what happens across periods and 2) what happens within the period.

What happens across periods. The HBT uses Leaky Bucket counters [24] to detect if a branch mispredicts at a rate higher than the AMR. As mispredicted branches retire, a counter stored in the HBT is incremented. The counter is decremented periodically at a rate equal to the AMR. In this scheme, all branches that have a misprediction rate higher than the AMR will (eventually) saturate their counters (i.e., fill the Leaky Bucket), while branches that have a misprediction rate lower than the AMR will eventually saturate to 0 (Empty Bucket). The simplest way to decrement the counter at this rate is to decrement at the end of each period by  $AMR \times D$ .

$DecrementRate = AMR \times D$

What happens within the period. Decrementing the counter at

<sup>&</sup>lt;sup>2</sup>Time can be measured by counting the number of retired instructions, retired branch instructions, or retired mispredictions. However, the AMR must be adjusted accordingly.

the end of each period only works as expected if the counter does not saturate during the given period. If the counter were to saturate during the period, this would throw off the effective increment rate, which could potentially increase the impact of the decrement rate, leading to poor classification of hard-to-predict branches.

Therefore, we must ensure that the counter is wide enough (i.e., enough bits) such that the probability of saturating the counter in one period is sufficiently low. This probability is referred to as the probability of a false positive (PFP). To find the desired width we must first compute the probability of saturating the counter. To compute that, we model the sequence of mispredicting branches as a Binomial Distribution. The Binomial Distribution is used to represent the string of mispredicted/correctly predicted branches within the period (1 means mispredicted, 0 means correctly predicted). Each Binomial computes the probability that i mispredictions occurs. We then sum these probabilities for all i large enough to saturate a k-bit counter.

$$CounterBits = log_2(k+1)$$

for the smallest value k such that

$$PFP > \sum_{i=k}^{D} {D \choose i} p^{i} (1-p)^{(D-i)}$$

This arithmetic model leads to counters that are wide enough such that they have a very low likelihood of saturating spuriously, while also minimizing the counter width to not create more hardware cost or warm-up time than what is necessary. The arithmetic model essentially transforms parameters like decrement rate and counter width, parameters that can feel arbitrary to assign values to, to parameters that are more human relatable, like acceptable misprediction rate (AMR) and probability of a false positive (PFP). This gives architects more control over the parameters of the HBT, without requiring simulation sweeps for fine tuning.

#### 2.3.2 Hard Branch Table

The final resulting piece of hardware derived from the equations above turns out to be relatively simple. Throughout this dissertation, we use a Hard Branch Table that is 64 entries large. The table is indexed and tagged with the PC of the branch instruction. At each location, there is a 5-bit saturating misprediction counter. The misprediction counter is incremented each time a corresponding branch misprediction is retired. All counters are decremented by 15 after 1000 global branch mispredictions are retired. These numbers correspond to a Hard Branch Table with a AMR of 1.5%, a period of 1000, and a PFP of 1%.

## 2.4 Branch Cost

Branch mispredictions are not all created equal. To illustrate this, let's consider the following example.

Consider a theoretical machine that has a perfect i-cache, perfect d-

cache, perfect target predictor, 16-wide fetch/decode/rename, and contains 12 pipeline stages before execution. This same machine has a branch predictor that is 95% accurate. What is the maximum utilization of such a machine?

Assuming 1 out of every 5 instructions is a branch, and given that 1 out of ever 20 branches is a misprediction, we can therefore infer that 1 out of every 100 instructions will be a branch misprediction. With a 16-wide fetch unit we are able to reach the mispredicting branch after 7 cycles (100/16 = 6.25). Given that the pipeline contains 12 stages before execution, the minimum latency of the branch is 12 cycles. Therefore every 7 cycles there will be a 12 cycle period where we fetch no useful instruction. This puts machine utilization at 7/(7+12) or about 36.8%.

More generically, machine utilization can be given by the following ratio between useful cycle: wasted cycles.

$$Utilization = \frac{5(1-a)^{-1}}{W} : L$$

Where a is the branch predictor accuracy, W is the machine width, and L is the branch execution latency. This ratio makes clear why branch mispredictions increasingly become a bottleneck as machine width and depth increase. As machine width increases, we more quickly fetch our way through correct path instructions, reducing the total number of correct path cycles. While as the pipeline becomes deeper, we increase the minimum latency of a misprediction, thereby increasing the minimum latency of a branch misrpedic-

tion.

This example is also meant to illustrate that the waste created by a branch misprediction increases as the latency of the misprediction increases. Therefore, considering the accuracy of branch is only half the story. One must also consider a branch's expected latency to truly determine the expected branch misprediction cost.

## 2.5 Detecting Branches with High Branch Cost

Branch latency plays a key role in branch cost; however, latency and misprediction rate alone do not describe the full picture. Complex interactions in the pipeline, such as i/d-cache misses and full window stalls also impact branch cost. Deriving a formula that accounts for all involved variables is complex and unnecessary. Instead, branch cost can be measured directly by counting the number of micro-ops that are flushed from the Re-order Buffer (ROB) due to a retired branch misprediction.

Each flushed instruction represents a single unit of wasted fetch bandwidth due to the branch misprediction. The total number of flushed micro-ops represents the total wasted fetch bandwidth due to the branch misprediction and fully accounts for all complex pipeline interactions. The total number of flushed miro-ops can be quickly computed by subtracting the tail pointer for the ROB with the ROB ID of the branch instruction. Note that to truly account for all wasted fetch bandwidth, micro-ops flushed from fetch, decode, rename, and any other stages that come before ROB allocation should also be

accounted for. Counting this additional micro-ops, however, adds unnecessary complexity to the pipeline. Simply counting the micro-ops flushed from the ROB is sufficient for estimating wasted fetch bandwidth.

#### 2.5.1 Branch Cost Table

Integrating branch cost into the HBT is a trivial task. Whereas before we treated all branch mispredictions equally, now each misprediction is weighted by the branch cost. When a branch misprediction occurs, the number of micro-ops flushed from the ROB is computed. Then, rather than incrementing the HBT misprediction counter by 1, the counter is incremented by branch cost. Furthermore, the decrement rate and the HBT counter width need to be increased to reflect the new increment rate.

## 2.6 Related Work

There are many other confidence estimations techniques not directly addressed in this dissertation. However, all techniques suffer from the issues described above. Jim Smith uses the magnitude of the saturating counter in the bimodal table to estimate branch confidence [55]. While this method is useful in that it requires no modification on top of a baseline branch predictor (and was later extended to TAGE [51]), this confidence mechanism is still limited to assigning confidence to particular predictions from the branch predictor. Further, because it is tied to the state of single bimodal table, it adapts too quickly to recent branch behavior. The accuracy of these technique can

be improved by using either a path history [19, 20, 36] or Perceptrons [4, 27]; however, these improvements do not address the limiting issues with these technique.

### 2.7 Future Work

One limitation of the Hard Branch Table is its small size. While this is not a problem for SPEC or Graph workloads, workloads that have larger instruction footprints may have issues fitting in the small HBT. Large instruction footprint can impact the HBT in two areas. First, it can impact the replacement policy of Hard Branches. Currently, branches are replaced when their misprediction counter is zero. However, in large instruction footprint applications the effective reuse distance of branches is much larger, which can make caching a set of them in a small cache more difficult. Therefore, a separate aging mechanism is needed to retain branches that have not been seen recently.

Second, a large instruction footprint can lead to a large number of branches that reach the minimum threshold requirements for making it in the HBT. Therefore, a dynamically adapting AMR threshold is needed to raise the threshold such that only the hardest to predict branches in the workload are able to enter into the table. In this model, the AMR would start off high. Occupancy of the table would then be monitored. If not enough branches are able to overcome the high threshold (and therefore the occupancy of the HBT is low), then the AMR will by dynamically lowered. This will allow more

branches into the table. This process will be repeated until the occupancy reaches a desired threshold.

# Chapter 3

# Merge Point Prediction

## 3.1 Introduction

This chapter discusses dynamic merge point prediction as a runtime alternative to branch prediction.<sup>1</sup> By predicting the merge point of a branch, the processor can avoid an expensive branch misprediction, instead utilizing a control independence strategy [13, 47, 25, 50, 56, 37, 14, 42, 43, 6, 48]. A control independence strategy is a technique that does not require knowledge of the branch direction, but can be used to mitigate or avoid a branch misprediction. This chapter proposes and evaluates a fundamentally new algorithm for detecting merge points. Prior approaches use compiler heuristics and assumptions about code layout to predict the location of the merge point that result in limited accuracy and coverage. My work takes advantage of branch mispredictions by comparing instructions fetched from the wrong path and correct path to detect the merge point. I argue this new approach to merge point prediction is fundamentally more accurate and reliable than prior work.

The merge point predictor is able to achieve an average accuracy of 95% across the SPEC CPU2006 benchmark suite [3]. The improved accuracy

<sup>&</sup>lt;sup>1</sup>The ideas presented in this Chapter were first published in [44], which is my own work.

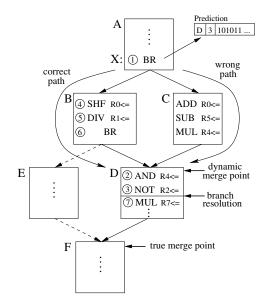

Figure 3.1: Example Control Flow Graph (CFG)

Dashed edges indicates paths that are rarely traversed at runtime. The compiler would report that the merge point of A is F. However, because block E is rarely seen, D is predicted as the merge point.

results in successfully detecting and replacing 58% of all branch mispredictions with a correct merge point prediction, reducing the MPKI by an average of 43%.

## 3.2 Motivation

The merge point predictor is designed with common control independence techniques in mind [13, 47, 25, 50, 56, 37, 14, 42, 43, 6, 48]. My work emphasizes three key principles that I believe to be essential for utilizing control independence effectively. First, only hard-to-predict or long latency branches are candidates for merge point prediction. We only consider merge

point prediction an option when a branch misprediction is too risky. Second, predicted merge points should be as close to the branch as possible. Often, the merge point predictor identifies more than one potential merge point for a given branch. This is because the merge point predictor is identifying dynamic merge points, which will be explained later in this section. Selecting merge points that are closer to the branch increases the number of post merge point instructions that are control and data independent of the branch. Furthermore, it decreases the number of resources that are required by the merge point, which reduces the size of reservations required by some control independence strategies. Third, merge point predictions must be accurate. If a merge point prediction is wrong, then the machine must be flushed, similar to a branch misprediction. We design a highly accurate dynamic merge point predictor that generates predictions at runtime without relying on compiler input or code layout<sup>2</sup>. Prior predictors [13, 15] make assumptions about compilers and code layout, making their work inaccurate and resistant to change. Our predictor takes advantage of branch mispredictions, finding the point where correct-path and wrong-path converge, making our predictor oblivious to compiler changes.

#### 3.2.1 Weaknesses of Detecting Merge Points at Compile Time

The compiler itself could be used to easily identify merge points with 100% accuracy, however highly biased branches can weaken the compiler's

<sup>&</sup>lt;sup>2</sup>Arrangement of basic blocks in memory

ability to find the nearest merge point [28, 15], which can negatively affect performance. Furthermore, identifying hard-to-predict branches at compile time is difficult, reducing the compiler's ability to provide help where it is most needed. Finally, compilers require costly instruction-set support to communicate with the microarchitecture that would likely result in additional fetch bandwidth being wasted.

The dynamic merge point predictor uses run-time information to find the nearest merge point. For example, consider the control-flow graph (CFG) shown in Figure 3.1. A compiler would identify block F as the merge point, because it is the only block guaranteed to execute after A. However, highly biased branches can effectively remove edges from the CFG. To illustrate this, Figure 3.1 uses dashed edges to identify branch directions that are rarely taken at run-time. If these edges are omitted, then block D becomes the merge point. Predicting block D as the merge point yields a merge point that is closer to the branch, but is sometimes inaccurate. Predicting block F is always correct, but is farther away than block D, making it less useful for performance.

Highly skewed branches prune edges of the CFG, producing merge points that are closer to branches. Our experiments show that 61% of conditional branches never change direction while an additional 9% of branches change direction <1% of the time <sup>3</sup>. The large number of highly biased branches suggests that identifying merge points at runtime will have a ma-

<sup>&</sup>lt;sup>3</sup>Measured across the SPEC CPU2006 [3] benchmark suite

jor advantage over compile time.

## 3.2.2 Weaknesses of Prior Work in Merge Point Prediction

The previous state-of-the-art merge predictor proposed by Collins et al. [15] has several major weaknesses. First, their predictor is not a general solution. It is a collection of three heuristics that all rely on the compiler to generate code that fits into their model. As compilers change over time, their predictor may become less accurate. In contrast, our algorithm leverages branch mispredictions to find the place where the wrong path and the correct path overlap. We do not rely on compiler heuristics, which enables us to cover a lot more cases and achieve higher accuracy. In our experiments, we compare to the infinitely sized, unrealistic predictor proposed by Collins et al. Despite their model having an unrealistic storage budget, their model achieves an average accuracy of only 78% across the branch intensive workloads in SPEC 2006. Our realistic 4KB predictor achieves an accuracy of 95% on those same workloads.

These numbers do not match the numbers reported by Collins et al. In their paper [15], the authors report an accuracy of 95% for their infinitely sized predictor, however, our evaluation shows an accuracy of at most 78%. We have accounted for the discrepancy and attribute it to two factors. First, we do not account for branches with trivial merge points that are are unlikely to be mispredicted. Examples of this are constant length loop branches and function calls. In both cases, the merge point is trivial to predict, boosting the

accuracy of the merge predictor. However, in both cases the branch direction is also trivial to predict, meaning that there will likely not be a branch direction misprediction. If the branch predictor is correct, we will not make use of the predicted merge point, making the correct merge point prediction meaningless. We therefore do not count easy-to-predict loop branches and function calls as part of accuracy. In our system, only branches with low branch prediction confidence make use of the merge point predictor. Due to the high frequency of loop branches, removing them from consideration significantly lowers relevant accuracy. Second, we enforce all merge points identified by both predictors be points where control converges. Due to the methodology used in [15], some of the predicted values are not true merge points, but rather random intermediate places in the control flow graph. In our methodology, these points are counted as incorrect for both predictors.

## 3.3 Dynamic Merge Point Prediction

A merge point prediction consists of three parts: the PC of the merge point, the merge distance, and the independent register set. The merge distance is the predicted number of dynamic instructions in which the merge point is expected to be found. The predicted distance can be used to identify merge point mispredictions, and also serves to place an upper bound on the number of instructions between the branch and the merge point, which may be useful for some control independence strategies. The independent register set is the set of architectural registers that are predicted to be independent of the branch. Post merge point instructions that source registers identified by the independent register set do not have any data-dependencies with instructions between the branch and its merge point.

### 3.3.1 Merge Predictor Design

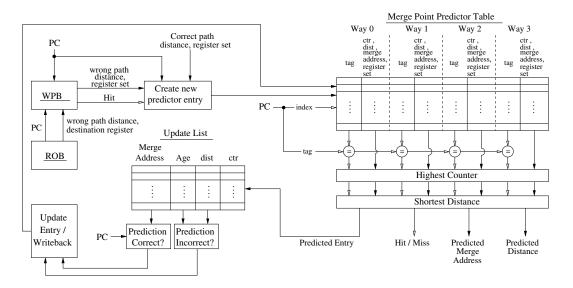

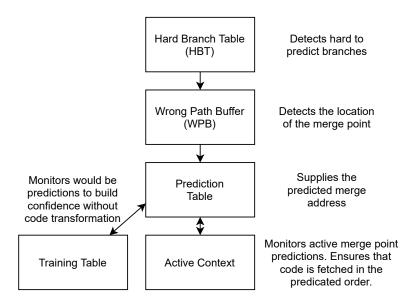

The merge predictor design consists of three new structures: the Merge Point Predictor Table, the Update List, and the Wrong Path Buffer (WPB). Figure 3.2 shows a block diagram of all three structures. The WPB is responsible for detecting new merge points and installing them into the predictor table. The update list is responsible for tracking predicted entries and updating them appropriately.

Merge points are detected by observing both the wrong-path and correctpath of a branch. When a branch misprediction occurs, wrong-path instructions are copied from the Reorder Buffer (ROB) to the WPB. After the machine is flushed, each retired, correct-path instruction accesses the WPB. If

there is a hit, then a new merge point has been found and is installed into

the predictor table. Next time the branch is fetched, the predictor table supplies the merge point and an entry is allocated in the update list. When the

branch retires, it activates its entry in the update list. Once activated, the

update list entry monitors retiring instructions. If the predicted merge point

retires within the merge distance without any unexpected register writes, then

the prediction is correct, otherwise it is incorrect. In either case, the entry is

updated and then removed from the update list.

Figure 3.2: All three newly added structures: Merge Predictor Table, Update List and WPB.

Figure 3.2 shows the interactions between the three newly added structures and the ROB. The Predictor Table supplies the predicted entry to the Update List. The Update List compares entires to retired PCs until the merge point is confirmed or the merge distance is reached. At this point, the entry is updated and written back to the predictor. The Wrong Path Buffer (WPB) saves wrong-path PCs, supplied by the ROB, and compares them to correct-path PCs. When a match is found a new entry is installed in the predictor.

Section 3.3.1.1 discusses how new merge points are detected. Next, 3.3.1.2 discusses the implementation of the WPB. Section 3.3.1.3 discusses how predictions are made. Finally, section 3.3.1.4 discusses how the predictor is updated.

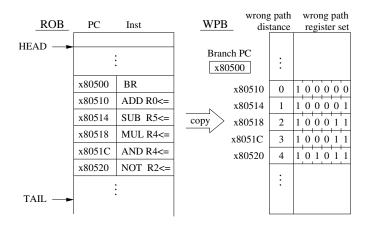

#### 3.3.1.1 Detecting New Merge Points

Our design detects new merge points by exploiting branch mispredictions. Due to the large size of instruction windows and high fetch rates, it is common for processors to fetch many wrong-path instructions before detecting a misprediction. Our experiments show an average of 100 dynamic instructions fetched on the wrong path. Upon detecting a branch misprediction, wrong path instructions must be copied from the ROB into the WPB. Figure 3.3 shows an example. Instructions are copied from the ROB starting with the first instruction after the mispredicted branch, and ending upon one of three conditions: (1) there are no more instructions in the ROB, (2) the maximum merge distance is reached, or (3) another instance of the same branch is encountered in the ROB (i.e., a loop back to the branch). Instructions are copied from the ROB to the WPB by conducting a ROB-walk during the flush.<sup>4</sup> Each wrong-path instruction indexes the WPB with its PC and stores a wrong-path distance number and a bit-vector called the wrong-path independent register set. The distance number represents the number of dynamic instructions between the current instruction and the branch, while the independent register set represents the accumulated destination registers of each instruction up to this point. Finally, we tag the WPB with the PC of the mispredicting branch, and set a valid bit, indicating that the WPB should be compared to future

<sup>&</sup>lt;sup>4</sup>We do not expect the ROB-walk latency to be an issue. It is not unusual for ROB-walks to be used during a flush to restore the state of the speculative register alias table. Furthermore, latency of ROB-walks are typically hidden by the front-end as it refills the pipeline.

Figure 3.3: Wrong-path instructions copied from the ROB to the WPB

When the branch (PC=x80500) misprediction is detected, subsequent instructions are copied from the ROB to the WPB. The distance between the branch and each instruction is saved in the WPB. Additionally, the destination register of each instruction is saved in the the wrong-path register set bit-vector.

retired instructions.

After populating the WPB and flushing the machine, fetch is redirected down the correct path. When correct-path instructions retire, their program counters are used to index into all of the valid WPBs. Similar to filling the WPB, we continue until one of three conditions is met: (1) a PC hits in the WPB (2) the maximum merge distance has been reached or (3) the PC is equal to the PC of the mispredicted branch<sup>5</sup>. If there is a match (i.e., option 1), then we have found a merge point and install a new entry into the predictor table. If either option 2 or 3 occurs before finding a match, then we assume

$<sup>^{5}</sup>$ This happens when there is a loop back to the branch before encountering the merge point.

that there is no merge point and invalidate the WPB. Each WPB maintains a count of correct-path instructions that have indexed it called the correct path distance. Additionally, the WPB also tracks the correct-path independent register set by accumulating the destination registers of retired instructions into a bit vector.

Upon a WPB hit, the wrong-path distance and wrong-path independent register set are read from the WPB. The merge point is identified by the PC that hit in the WPB. The predicted distance is set to the larger of the wrong path distance and the correct path distance. Finally, the independent register set is formed by ORing the wrong-path bit vector and the correct-path bit vector. The entry is then installed into the predictor table and the WPB is invalidated.

#### 3.3.1.2 Design of the WPB

Ideally the WPB would be a fully associative CAM; however, large CAMs are impractical. For that reason, we chose to implement the WPB as a 128-entry 4-way set associative cache. Organizing the WPB as a cache instead of a CAM creates the possibility for an entry to be evicted, creating false negatives. In our evaluation, we observed less than 1% false negative rate, which led to an almost negligible loss in coverage. The WPB uses the MRU replacement policy.

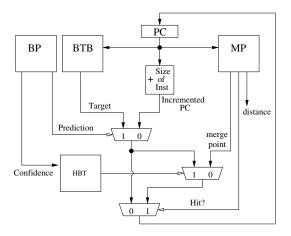

Figure 3.4: Interaction between the Branch Predictor (BP), Branch Target Buffer (BTB), and Merge Predictor (MP).

### 3.3.1.3 Making the Prediction

The PC is used to access the merge predictor in parallel with the branch target buffer (BTB) and the branch predictor. Figure 3.4 shows the connections between each of these structures. The entry supplied by the merge predictor is only considered if the Hard Branch Table (HBT) has identified the branch as hard-to-predict. The merge predictor is accessed as a typical set associative cache. If there is a miss, we defer back to the branch predictor.

If there is a hit, it is possible that multiple entries match the branch address. For example, consider the CFG in Figure 3.1. As discussed in section 3.2, the merge point of the branch in basic block A could either be D or F. It is possible that both D and F are detected by the WPB and are both installed into the predictor. In the event that two or more entries match in the predictor, the 3-bit saturating counter is examined and the entry with the

highest counter value is selected as the prediction. If two or more entries have equal counter values, then the merge entry containing the minimum merge distance is selected. We choose the entry with the minimum merge distance because predicting smaller distances results in smaller reservations in the instruction window. Once an entry has been selected for prediction, all entries that matched in the predictor are inserted into the Update List.

When new entries are installed into the predictor, it may be necessary to evict an older entry. Entries with the smallest counter value are the first victims for eviction. If all entries have equal counters, then the entry with the largest predicted distance value is selected as the victim.

## 3.3.1.4 Updating the Predictor

Once inserted into the update list, entries wait until the merge-predicted branch instruction reaches retire. At that point, the update list entry becomes active. An Update List entry contains the following information: (1) the PC of the merge-predicted branch, (2) a prediction age field, which is the number of dynamic instructions retired since the entry became active, and (3) the predictor table entry that will be updated and written back to the predictor. An entry remains in the Update List until either (1) a PC matching the merge address is found (meaning the prediction is correct), (2) the age field exceeds the merge distance (the prediction is incorrect), or (3) the PC of the

merge-predicted branch is seen retiring for a second time<sup>6</sup> (the prediction is incorrect). If the prediction is correct, the 3-bit saturating counter is incremented, otherwise the counter is decremented. Additionally, the destination registers of gap instructions are monitored. If any unexpected writes occur<sup>7</sup>, then the prediction is considered incorrect and the machine is flushed.