# Performance Prediction for Dynamic Voltage and Frequency Scaling

Rustam Raisovich Miftakhutdinov

High Performance Systems Group Department of Electrical and Computer Engineering The University of Texas at Austin Austin, Texas 78712-0240

> TR-HPS-2014-004 August 2014

This page is intentionally left blank.

Copyright by Rustam Raisovich Miftakhutdinov 2014 The Dissertation Committee for Rustam Raisovich Miftakhutdinov certifies that this is the approved version of the following dissertation:

# Performance Prediction for Dynamic Voltage and Frequency Scaling

Committee:

Yale N. Patt, Supervisor

Robert S. Chappell

Derek Chiou

Mattan Erez

Donald S. Fussell

# Performance Prediction for Dynamic Voltage and Frequency Scaling

by

## Rustam Raisovich Miftakhutdinov, B.S.E.E., M.S.E.

### DISSERTATION

Presented to the Faculty of the Graduate School of The University of Texas at Austin in Partial Fulfillment of the Requirements for the Degree of

### DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT AUSTIN

December 2014

## Preface

One of the biggest and most important tools of theoretical physics is the wastebasket.

**Richard Feynman**

This dissertation is a culmination of three years of work, from Summer 2011 to Summer 2014. Although not a theoretical physicist, I spent much of that time true to the words of Richard Feynman—struggling to solve problems I ended up discarding. The time I spent on these discarded problems was, however, not in vain. Little by little, each one contributed to my broader understanding and, in the end, allowed me to formulate and solve the problem of this dissertation.

Many people have helped me along the way and I would like to acknowledge their contributions.

I would like to thank my advisor, Dr. Yale N. Patt, for the opportunity and advice he gave me and the patience he afforded me.

I would like to thank the rest of my doctoral committee, Dr. Robert S. Chappell, Dr. Derek Chiou, Dr. Mattan Erez, and Dr. Donald S. Fussell for their feedback on my research. I would like to thank Rob Chappell in particular for introducing me to my dissertation topic during my summer internship at Intel in 2011.

I would like to thank the many present and former members of the HPS research group that helped me in my research pursuits. Specifically, I would like to thank

- Eiman Ebrahimi, Onur Mutlu, and Francis Tseng for working with me on my research problems,

- José Joao for sacrificing his time to maintain the IT infrastructure of the research group,

- Rob Chappell, Chang Joo Lee, Hyesoon Kim, Onur Mutlu, Paul Racunas, and Santhosh Srinath for significant contributions to my simulation infrastructure, and

- Marco Alves, Eiman Ebrahimi, Faruk Guvenilir, Milad Hashemi, José Joao, Khubaib, Hyesoon Kim, Peter Kim, Ben Lin, Veynu Narasiman, Moin Qureshi, Aater Suleman, Francis Tseng, and Carlos Villavieja for sharing their research ideas and discussing mine.

I would like to thank Melanie Gulick and Leticia Lira for helping me navigate the administrative bureaucracy of the university.

Finally, I would like to thank Muawya Al-Otoom, Hari Angepat, Abhishek Das, Mark Dechene, Chris Fallin, Andy Glew, Min Jeong, Maysam Lavasani, Ikhwan Lee, Nikhil Patil, Mike Sullivan, Dam Sunwoo, Birgi Tamersoy, Gene Wu, and Dan Zhang for many intellectual discussions (research-related and otherwise).

Rustam Miftakhutdinov August 2014, Austin, TX

# Performance Prediction for Dynamic Voltage and Frequency Scaling

Publication No. \_\_\_\_\_

Rustam Raisovich Miftakhutdinov, Ph.D. The University of Texas at Austin, 2014

Supervisor: Yale N. Patt

This dissertation proves the feasibility of accurate runtime prediction of processor performance under frequency scaling. The performance predictors developed in this dissertation allow processors capable of dynamic voltage and frequency scaling (DVFS) to improve their performance or energy efficiency by dynamically adapting chip or core voltages and frequencies to workload characteristics. The dissertation considers three processor configurations: the uniprocessor capable of chip-level DVFS, the private cache chip multiprocessor capable of per-core DVFS, and the shared cache chip multiprocessor capable of per-core DVFS. Depending on processor configuration, the presented performance predictors help the processor realize 72–85% of average oracle performance or energy efficiency gains.

# Table of Contents

| Prefac  | e                                                         | vi       |

|---------|-----------------------------------------------------------|----------|

| Abstra  | act                                                       | viii     |

| List of | Tables                                                    | xii      |

| List of | Figures                                                   | xiii     |

| Chapt   | er 1. Introduction                                        | 1        |

| Chapt   | er 2. Background                                          | <b>5</b> |

| 2.1     | Dynamic Voltage and Frequency Scaling                     | 5        |

| 2.2     | Performance Prediction                                    | 7        |

| 2.3     | Notational Conventions                                    | 8        |

| 2.4     | DRAM                                                      | 8        |

| 2.5     | Stream Prefetching                                        | 11       |

| Chapt   | er 3. Uniprocessor                                        | 13       |

| 3.1     | Background                                                | 14       |

|         | 3.1.1 Linear Model                                        | 14       |

|         | 3.1.2 Leading Loads                                       | 16       |

|         | 3.1.3 Stall Time                                          | 17       |

| 3.2     | CRIT: Accounting for Variable Access Latency Memory       | 17       |

|         | 3.2.1 Experimental Observations                           | 18       |

|         | 3.2.2 Variable Access Latency View of Processor Execution | 20       |

|         | 3.2.3 Hardware Mechanism                                  | 21       |

|         | 3.2.4 Summary                                             | 23       |

| 3.3     | BW: Accounting for DRAM Bandwidth Saturation              | 23       |

|         | 3.3.1 Experimental Observations                           | 24       |

|         | 3.3.2 Limited Bandwidth Analytic Model                    | 29       |

|         | 3.3.3 Parameter Measurement                               | 31       |

|         | 3.3.4 Hardware Cost                                       | 36       |

| 3.4     | Methodology                                               | 38       |

|        | 3.4.1  | Efficiency Metric                                                     |

|--------|--------|-----------------------------------------------------------------------|

|        | 3.4.2  | Timing Model                                                          |

|        | 3.4.3  | Power Model                                                           |

|        | 3.4.4  | DVFS Controller                                                       |

|        | 3.4.5  | Offline Policies                                                      |

|        | 3.4.6  | Benchmarks                                                            |

| 3.5    | Resul  | ts $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $43$                  |

|        | 3.5.1  | CRIT (Prefetching Off) 44                                             |

|        |        | CRIT+BW (Prefetching On)                                              |

| 3.6    | Concl  | usions $\ldots$ $\ldots$ $\ldots$ $48$                                |

| Chapte | er 4.  | Private Cache Chip Multiprocessor 49                                  |

| 4.1    | Exper  | rimental Observations                                                 |

| 4.2    | Scarce | e Row Hit Prioritization                                              |

|        | 4.2.1  | Problem                                                               |

|        | 4.2.2  | Mechanism                                                             |

|        | 4.2.3  | Results                                                               |

|        | 4.2.4  | Impact on Performance Predictability                                  |

| 4.3    | Indep  | endent Latency Shared Bandwidth Model                                 |

|        | 4.3.1  | Applicability of Linear Model                                         |

|        | 4.3.2  | Overview of Analytic Model                                            |

|        | 4.3.3  | Core Model                                                            |

|        | 4.3.4  | Equal DRAM Request Service Time Approximation                         |

|        | 4.3.5  | Bandwidth Constraint                                                  |

|        | 4.3.6  | Combined Model                                                        |

|        | 4.3.7  | Solution                                                              |

|        | 4.3.8  | Approximations Behind ILSB                                            |

| 4.4    | Paran  | neter Measurement                                                     |

|        | 4.4.1  | Core Model Parameters                                                 |

|        | 4.4.2  | Maximum DRAM Bandwidth                                                |

| 4.5    | Metho  | dology                                                                |

|        | 4.5.1  | Metric                                                                |

|        | 4.5.2  | DVFS Controller                                                       |

|        | 4.5.3  | Simulation                                                            |

|        | 4.5.4  | Workloads                                                             |

|        | 4.5.5  | Frequency Combinations                                                |

|        | 4.5.6  | Oracle Policies                                                       |

| 4.6    |        | ts $\ldots$ $\ldots$ $\ldots$ $.$ $.$ $.$ $.$ $.$ $.$ $.$ $.$ $.$ $.$ |

| 4.7    |        | usions                                                                |

| Chapte | er 5. Shared Cache Chip Multiprocessor              | 83  |

|--------|-----------------------------------------------------|-----|

| 5.1    | Problems Posed by Shared Cache                      | 83  |

| 5.2    | Experimental Observations                           | 84  |

| 5.3    | Analysis                                            | 87  |

| 5.4    | Robust Mechanism                                    | 89  |

| 5.5    | Results                                             | 90  |

| 5.6    | Case Study                                          | 92  |

| 5.7    | Conclusions                                         | 94  |

| Chapt  | er 6. Related Work                                  | 95  |

| 6.1    | Adaptive Processor Control                          | 95  |

|        | 6.1.1 Taxonomy of Adaptive Processor Controllers    | 96  |

|        | 6.1.2 Performance Prediction                        | 97  |

|        | 6.1.3 Other Approaches                              | 99  |

| 6.2    | DVFS Performance Prediction                         | 100 |

| 6.3    | Analytic Models of Memory System Performance        | 100 |

| 6.4    | Prioritization in DRAM Scheduling                   | 102 |

| Chapt  | er 7. Conclusions                                   | 104 |

| 7.1    | Importance of Realistic Memory Systems              | 104 |

| 7.2    | Performance Impact of Finite Off-Chip Bandwidth     | 105 |

| 7.3    | Feasibility of Accurate DVFS Performance Prediction | 106 |

| Biblio | graphy                                              | 107 |

# List of Tables

| 3.1 | Applicability of leading loads                     | 19 |

|-----|----------------------------------------------------|----|

| 3.2 | Bandwidth bottlenecks in the uniprocessor          | 28 |

| 3.3 | Hardware storage cost of CRIT+BW                   | 37 |

| 3.4 | Simulated uniprocessor configuration               | 37 |

| 3.5 | Uniprocessor power parameters                      | 40 |

| 4.1 | Bandwidth bottlenecks in the private cache CMP     | 51 |

| 4.2 | Simulated private cache CMP configuration          | 74 |

| 4.3 | Core frequency combinations                        | 76 |

| 5.1 | Simulated shared cache CMP configuration           | 85 |

| 6.1 | Citations for prior adaptive processor controllers | 98 |

# List of Figures

| 2.1  | Processor and DVFS configurations addressed in this dissertation                                                                                            | 6  |  |  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|

| 2.2  | Qualitative relationship between row locality, bank level parallelism,<br>and the dominant DRAM bandwidth bottleneck                                        | 10 |  |  |

| 2.3  | Stream prefetcher operation                                                                                                                                 |    |  |  |

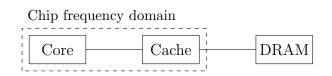

| 3.1  | Uniprocessor                                                                                                                                                | 13 |  |  |

| 3.2  | Linear DVFS performance model                                                                                                                               | 15 |  |  |

| 3.3  | Abstract view of out-of-order execution with a constant access latency memory system assumed by leading loads                                               | 16 |  |  |

| 3.4  | Abstract view of out-of-order processor execution with a variable la-<br>tency memory system                                                                | 20 |  |  |

| 3.5  | Critical path calculation example                                                                                                                           | 22 |  |  |

| 3.6  | Linear model applicability with prefetching off                                                                                                             | 25 |  |  |

| 3.7  | Linear model failure with prefetching on                                                                                                                    | 26 |  |  |

| 3.8  | Limited bandwidth DVFS performance model                                                                                                                    | 30 |  |  |

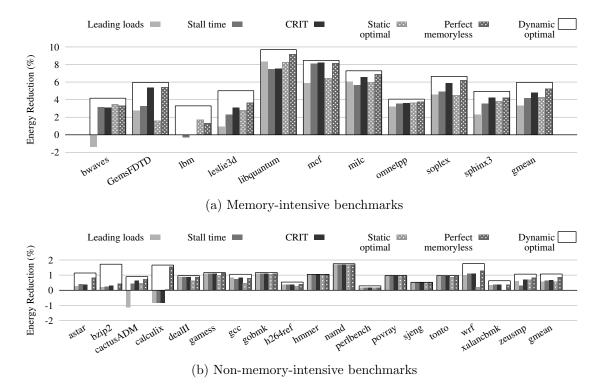

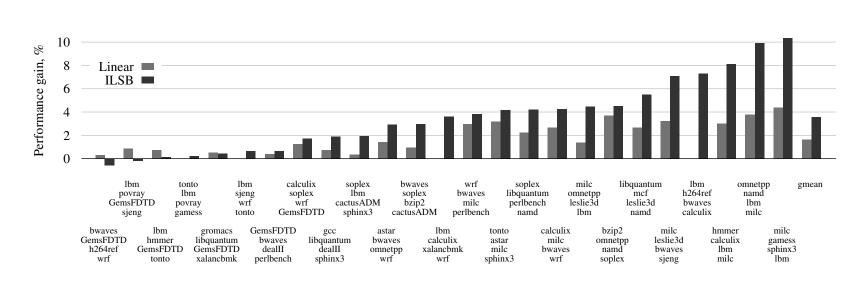

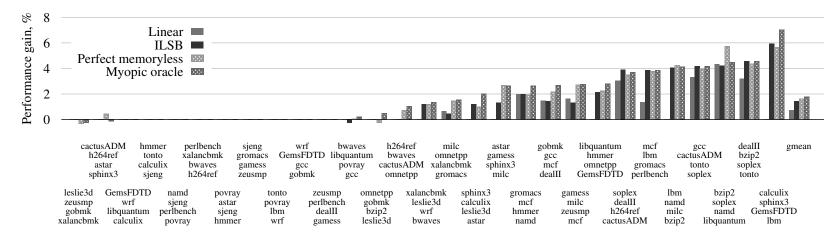

| 3.9  | Energy savings with prefetching off                                                                                                                         | 44 |  |  |

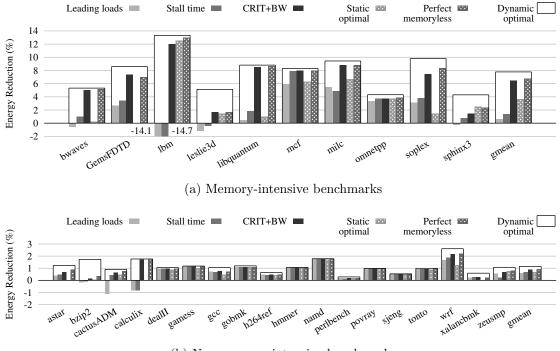

| 3.10 | Energy savings with prefetching on                                                                                                                          | 46 |  |  |

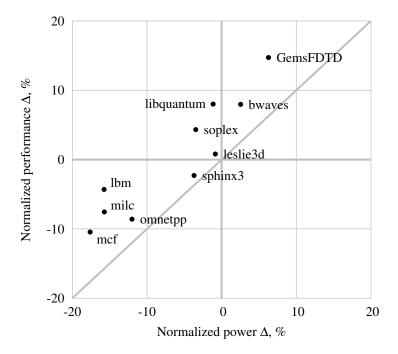

| 3.11 | Performance delta versus power delta under DVFS with CRIT+BW for memory-intensive benchmarks                                                                | 46 |  |  |

| 4.1  | Private cache CMP                                                                                                                                           | 49 |  |  |

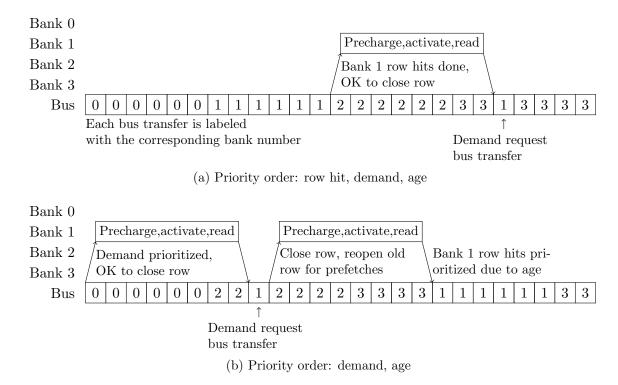

| 4.2  | Simplified timing diagrams illustrating DRAM scheduling under two different priority orders when row hits are abundant                                      | 52 |  |  |

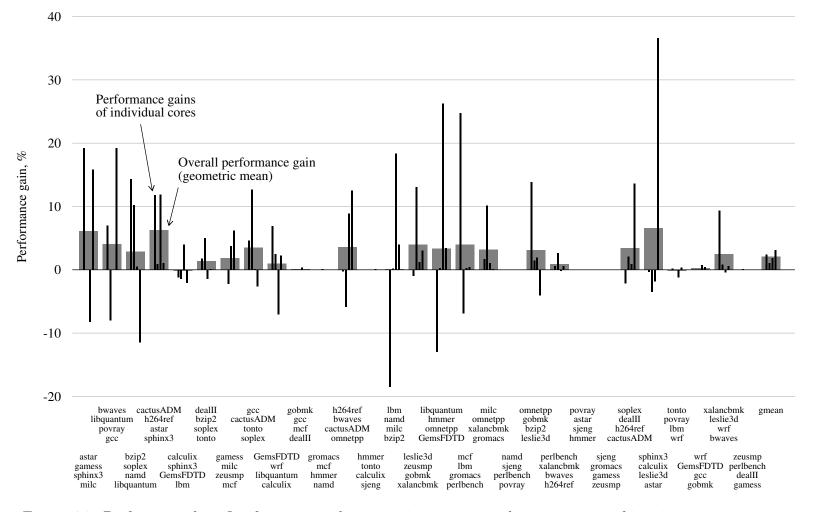

| 4.3  | Performance benefit of scarce row hit prioritization over indiscriminate row hit prioritization                                                             | 55 |  |  |

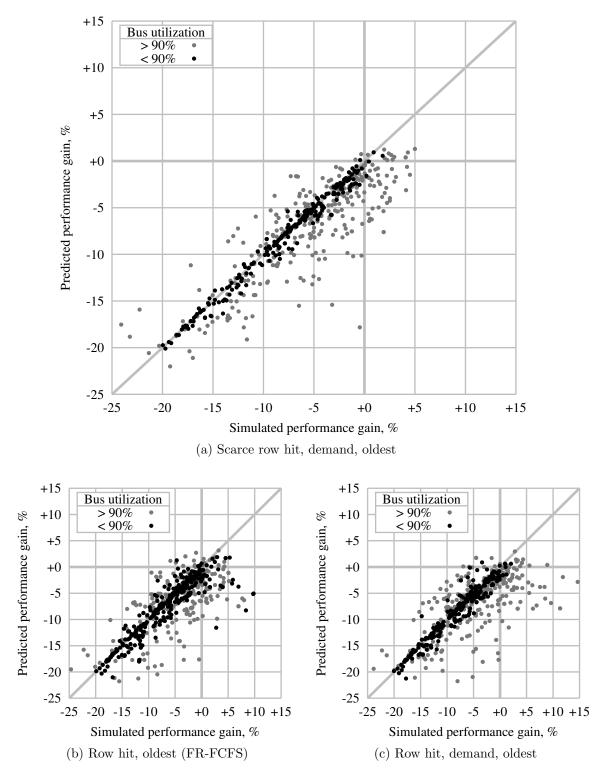

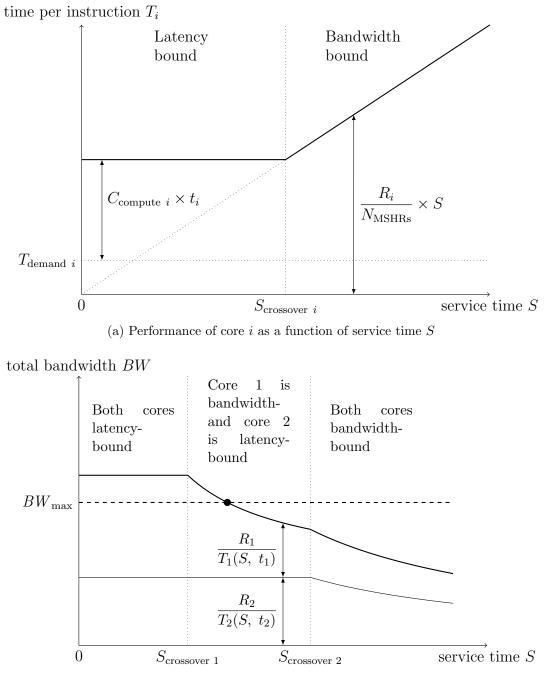

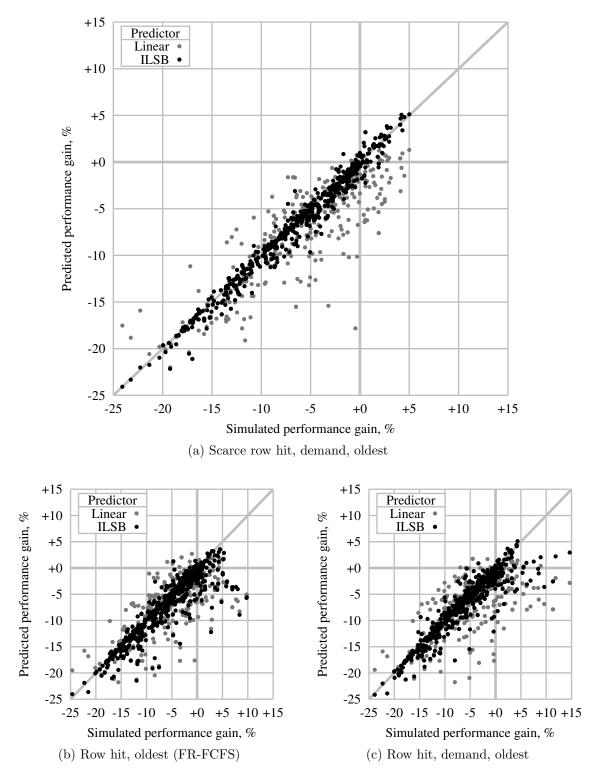

| 4.4  | Accuracy of the linear model applied to a four-core private cache CMP with three different DRAM scheduling priority orders                                  | 57 |  |  |

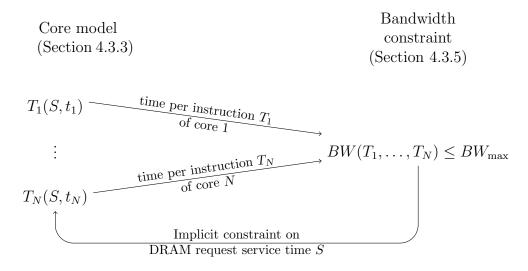

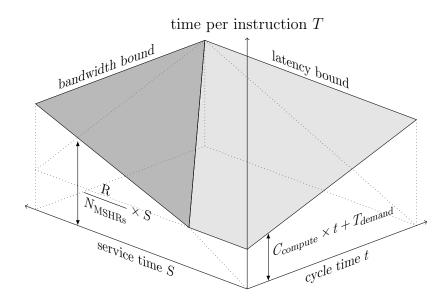

| 4.5  | High level structure of the ILSB analytic model                                                                                                             | 60 |  |  |

| 4.6  | Core analytic model                                                                                                                                         | 63 |  |  |

| 4.7  | Complete mathematical description of the independent latency shared<br>bandwidth (ILSB) model of chip multiprocessor performance under<br>frequency scaling | 65 |  |  |

| 4.8  | Graphical illustration of the independent latency shared bandwidth model applied to two cores                                                               | 67 |  |  |

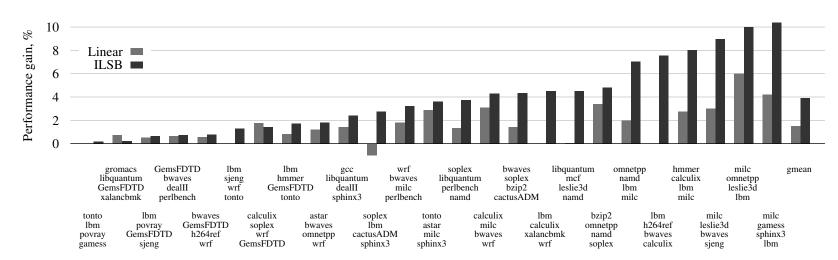

| 4.9  | Accuracy of the ILSB model and the linear model applied to a four-<br>core private cache CMP with three different DRAM scheduling priority<br>orders                   |    |  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

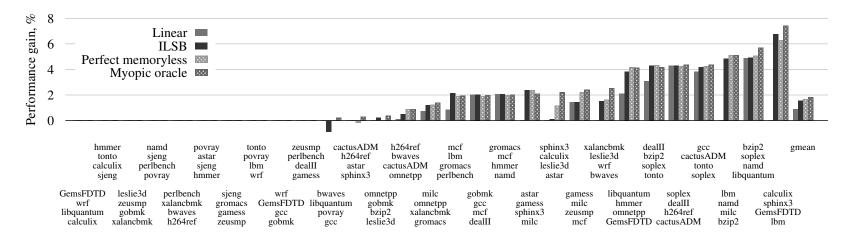

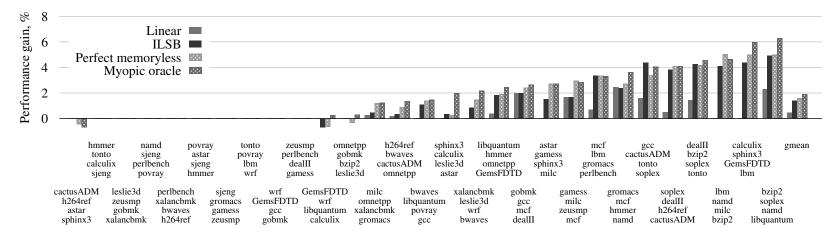

| 4.10 | Oracle performance study on private cache CMP (medium cores, 1 DRAM channel) with ALL workloads                                                                        | 80 |  |

| 4.11 | Full performance study on private cache CMP (medium cores, 1 DRAM channel) with BW workloads                                                                           | 80 |  |

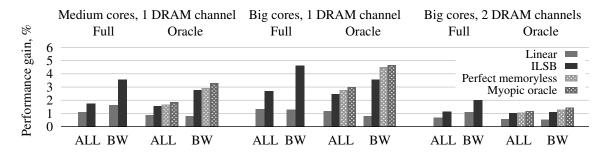

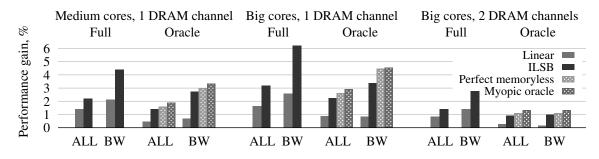

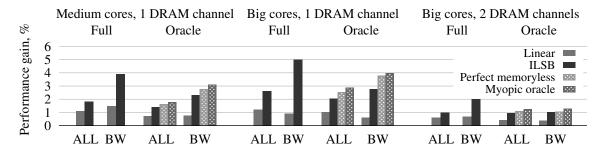

| 4.12 | Summary of experimental results for the private cache CMP $\ldots$ .                                                                                                   | 81 |  |

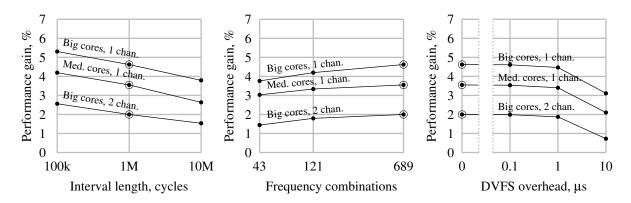

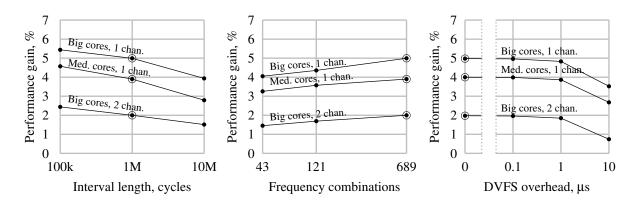

| 4.13 | Sensitivity studies for the private cache CMP with BW workloads                                                                                                        | 81 |  |

| 5.1  | Shared cache CMP                                                                                                                                                       | 83 |  |

| 5.2  | Summary of experimental results for our DVFS performance predictor<br>for the private cache CMP applied to the shared cache CMP                                        | 85 |  |

| 5.3  | Oracle performance study of our DVFS performance predictor for the private cache CMP applied to the shared cache CMP (medium cores, 1 DRAM channel) with ALL workloads | 86 |  |

| 5.4  | Full performance study of our DVFS performance predictor for the private cache CMP applied to the shared cache CMP (medium cores, 1 DRAM channel) with BW workloads    | 86 |  |

| 5.5  | Sensitivity studies of our DVFS performance predictor for the private cache CMP applied to the shared cache CMP with BW workloads                                      | 87 |  |

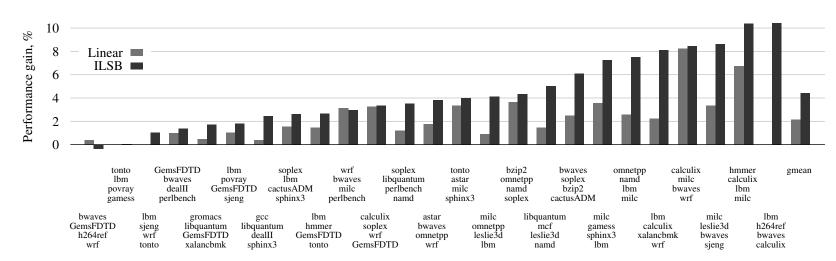

| 5.6  | Oracle performance study of our robust DVFS performance predictor<br>for the shared cache CMP (medium cores, 1 DRAM channel) with ALL<br>workloads                     | 91 |  |

| 5.7  | Full performance study of our robust DVFS performance predictor for<br>the shared cache CMP (medium cores, 1 DRAM channel) with BW<br>workloads                        | 91 |  |

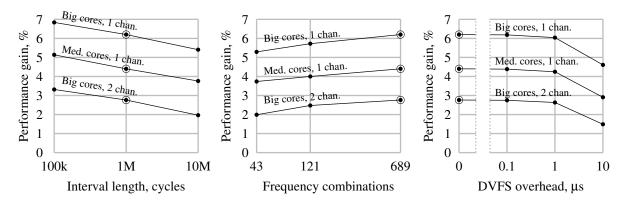

| 5.8  | Summary of experimental results for our robust DVFS performance predictor for the shared cache CMP                                                                     | 92 |  |

| 5.9  | Sensitivity studies of our robust DVFS performance predictor for the shared cache CMP with BW workloads                                                                | 92 |  |

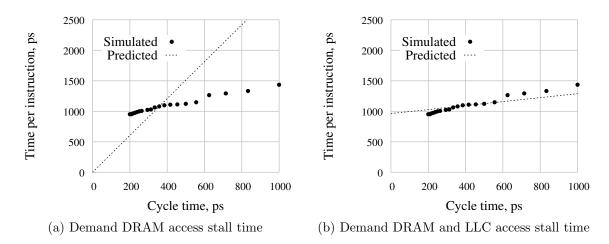

| 5.10 | Simulated and predicted performance of dep_chain versus core cycle time for two different $T_{\text{demand}}$ measurement mechanisms                                   | 93 |  |

| 6.1  | Taxonomy of adaptive processor control approaches                                                                                                                      | 96 |  |

## Chapter 1

## Introduction

Essentially, all models are wrong, but some are useful.

George E. P. Box

Dynamic voltage and frequency scaling (DVFS) presents processor designers with both an opportunity and a problem. The opportunity comes from the multitude of voltage and frequency combinations, or *operating points*, now available to the processor. The operating point that maximizes performance (within a power budget) or energy efficiency depends on workload characteristics; hence, with DVFS, the processor can improve its performance or energy efficiency by switching to the best operating point for the running workload. The problem is to identify which operating point is the best at any given time.

One way to solve this problem is to equip the processor with a *performance predictor*, a mechanism capable of predicting what processor performance would be at any operating point. So equipped, a processor can improve its performance by periodically switching to the operating point predicted to yield the highest performance for the running workload. To improve energy efficiency in the same way, the processor would also need a power consumption predictor; however, since power prediction is simple if accurate performance prediction is available,<sup>1</sup> in this dissertation we focus primarily on performance predictors.

A performance predictor consists of

<sup>&</sup>lt;sup>1</sup>Section 3.4.4 describes a power prediction scheme that relies on performance prediction.

- 1. a mathematical model that expresses processor performance as a function of the operating point and workload characteristics and

- 2. hardware mechanisms that measure these workload characteristics.

The model could be either

- *mechanistic*, that is derived from an understanding of how the mechanism (in our case, the processor) works, or

- *empirical*, that is based purely on empirical observations.

In this dissertation, we focus on DVFS performance predictors based on mechanistic models, which are more valuable than empirical models from a researcher's point of view. Most importantly, mechanistic models of processor performance advance our understanding of the major factors that drive processor performance, whereas empirical models, at best, merely show that performance is predictable without revealing why. Note that the assumptions underlying a mechanistic model may still be (and, in our case, often are) based on empirical observations.

This dissertation proves the feasibility of designing good DVFS performance predictors based on mechanistic models. We measure the goodness of a DVFS performance predictor by how well the predictor can guide DVFS; that is, how much of the benefit obtained by a hypothetical oracle predictor can the real predictor realize. In short, this dissertation proves the following thesis:

A performance predictor comprised of a mechanistic model and hardware mechanisms to measure its parameters can guide dynamic voltage and frequency scaling well enough to realize most of the benefit obtained by an oracle predictor.

To prove this thesis, we design and evaluate DVFS performance predictors for three processor configurations: the uniprocessor, the private cache chip multiprocessor, and the shared cache chip multiprocessor. In Chapter 3, we develop a performance predictor for the uniprocessor and use it to guide chip-level DVFS to improve energy efficiency. In Chapter 4, we develop a performance predictor for the private cache chip multiprocessor and use it to guide per-core DVFS to improve performance within a power budget. In Chapter 5, we show that the performance predictor for the private cache chip multiprocessor also works with a shared cache, explain why, and propose a more robust mechanism tailored for the shared cache configuration.

As we follow this path and develop new and more accurate DVFS performance predictors in the chapters ahead, we shall see two main points of focus emerge:

- 1. *Realistic memory systems.* We take care to consider the major features of modern memory systems:

- variable DRAM request latencies resulting from DRAM timing constraints and DRAM scheduler queuing delays,

- the commonly used stream prefetcher which may greatly increase DRAM bandwidth demand, and

- the prioritization of demand (instruction fetch and data load) requests in DRAM scheduling.

We pay particular attention to these details of modern memory systems because, as we shall soon see, memory system behavior largely determines the performance impact of frequency scaling—the same performance impact we want the processor to be able to predict.

2. Performance impact of finite bandwidth. As a result of our focus on the details of modern memory systems, we show that the commonly used stream prefetcher may lead to DRAM bandwidth saturation—an effect ignored by prior DVFS performance predictors. We design our DVFS performance predictors to take DRAM bandwidth saturation into account. For the uniprocessor, we model how finite bandwidth may limit processor performance. For the chip multiprocessor, we model how finite bandwidth, shared among the cores, may limit performance of some of the cores but not the others. These points of focus are the reason that the DVFS performance predictors we develop significantly outperform the state-of-the-art and deliver close to oracle gains in energy efficiency and performance.

## Chapter 2

## Background

Learning without thought is labor lost; thought without learning is perilous.

Confucius

In this chapter, we present some background information on dynamic voltage and frequency scaling, the general approach of performance prediction, notational conventions, DRAM, and stream prefetching. We shall rely on this background information to explain our performance predictors in Chapters 3, 4, and 5.

### 2.1 Dynamic Voltage and Frequency Scaling

Dynamic voltage and frequency scaling (DVFS) [5, 27] allows the processor to change the supply voltage and operating frequency (the combination of which we call an *operating point*) of the whole chip or its parts at runtime. Voltage and frequency are generally scaled together because higher frequencies require higher voltages. Generally, performance increases at most linearly (but often sublinearly) with frequency whereas power consumption increases roughly cubically with frequency. [57]

The variation in performance impact of DVFS is due to variation in workload characteristics. For example, if a workload accesses off-chip memory often, the performance impact of DVFS is sublinear because DVFS does not affect off-chip memory latency. On the other, if a workload never misses in the cache, the performance impact of DVFS is linear with frequency.

This variation in performance impact of DVFS means that the optimal operating point for the processor is workload-dependent. Whatever the target metric

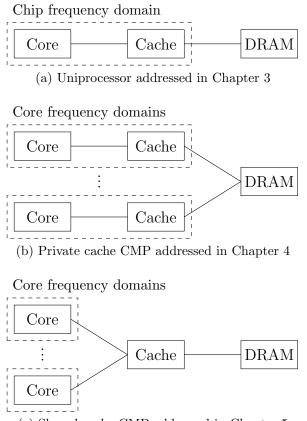

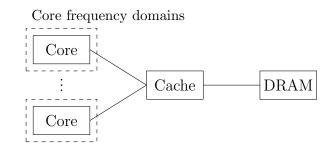

(c) Shared cache CMP addressed in Chapter 5

Figure 2.1: Processor and DVFS configurations addressed in this dissertation

(such as energy, performance, or energy-delay product), DVFS endows the processor with the capability to dynamically adjust its operating point in order to improve that target metric. This capability gives rise to the central problem of this dissertation: that of choosing the optimal operating point at runtime.

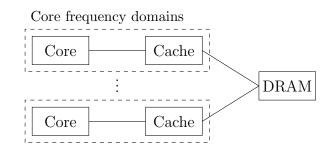

Traditionally, DVFS has been applied at the chip level only; recently, however, other DVFS domains have been proposed. David et al. [16] propose DVFS for off-chip memory and Intel's Westmere [45] supports multiple voltage and frequency domains inside the chip. In this dissertation, as illustrated in Figure 2.1, we focus on reducing energy consumption using chip-level DVFS (Chapter 3) and improving performance within the power budget using per-core DVFS (Chapters 4 and 5).

### 2.2 Performance Prediction

Performance prediction is a way to improve processor performance or energy efficiency by adapting some adjustable parameter of the processor to better suit workload characteristics. As discussed in Chapter 1, a performance predictor generally consists of a) a mathematical model that expresses performance as a function of the adjustable parameter and some workload characteristics, and b) hardware mechanisms that measure the necessary workload characteristics.

The processor uses the performance predictor to control the adjustable parameter as follows:

- 1. For one interval, the performance predictor measures workload characteristics needed.

- 2. At the end of the interval, the predictor feeds the measured workload characteristics into the performance model.

- 3. The performance model estimates what the processor performance would be at every available setting of the adjustable parameter.

- 4. The processor changes the adjustable parameter to the setting predicted to maximize performance (or another target metric) and the process repeats for the next interval.

All performance predictors considered in this dissertation operate in this fashion.

Note the assumption implicit in these steps: the workload characteristics measured during the previous interval are expected to remain the same during the next interval. We make this assumption because we focus on predicting performance given known workload characteristics; predicting what the workload characteristics in the next interval would be is the problem of phase prediction—a very different problem [29, 30, 74, 87] which lies outside the scope of this dissertation. Performance prediction has been used by prior work to dynamically control DVFS [10, 13–15, 18, 22, 37, 49, 61, 71], the number of running threads [82], shared cache partition [2, 66, 67], prefetcher aggressiveness [51], core structure sizes [19], DRAM bandwidth partition [53–55, 66, 67], and choice of core type in an asymmetric CMP [56, 86]. We present a more detailed overview of prior work on performance prediction in Chapter 6.

Two prior DVFS performance predictors are of particular interest to us: *lead-ing loads* [22, 37, 71] and *stall time* [22, 37]. These works are the only previously proposed DVFS performance predictors based on a mechanistic model. We describe these predictors in detail in Section 3.1.

#### 2.3 Notational Conventions

Performance prediction for DVFS and the associated mathematical models require nontraditional notation to express performance and frequency.

Traditionally, performance of a single application is expressed in instructions per cycle (IPC); however, this unit is inappropriate when chip or core frequencies are allowed to change. Therefore, in this dissertation, the fundamental measure of performance of a single application is instructions per unit time (IPT).

In addition, the mathematical models of performance under frequency scaling turn out to be easier to express not in terms of IPT and frequency, but rather in terms of their reciprocals. Specifically, we shall deal mostly with time per instruction (TPI) rather than IPT and cycle time rather than frequency.

### 2.4 DRAM

As we shall see later on, DRAM latency and bandwidth are important factors in processor performance, particularly under frequency scaling; thus we provide a brief overview of DRAM below. Modern DRAM systems [31, 58] are organized into a hierarchy of *channels*, banks, and rows.<sup>1</sup> Each channel has a data bus connected to a set of banks. Each bank contains many rows and can have a single row open at any given time in its row buffer. All data stored in DRAM is statically mapped to some channel, bank, and row.

To access data stored in DRAM, the DRAM controller issues commands to close (or "precharge") the open row of the relevant bank, open (or "activate") the row mapped to the data needed, transferring the row to the bank's row buffer, and read or write the data over the data bus. Subsequent requests to the same row, called *row hits*, are satisfied much faster by data bus transfers out of or to the row buffer.

Modern DRAM controllers typically prioritize row hit requests, demand (instruction fetch and data load) requests, and oldest requests. Row hit prioritization [70] exploits row locality in data access patterns to reduce DRAM access latency and better exploit DRAM bandwidth; demand prioritization helps shorten the latency of core stalls caused by demand accesses.

Much of this dissertation deals with the impact of limited DRAM bandwidth on processor performance; hence, we take a closer look at the three DRAM bandwidth constraints:

- 1. Row open bandwidth. The "four activate window" (FAW) constraint limits the rate at which rows of a channel may be opened by allowing at most four row opens ("activates") in any window of  $t_{\text{FAW}}$  consecutive DRAM cycles (where  $t_{\text{FAW}}$  is a DRAM system parameter).

- Bank bandwidth. The latencies needed to open, access, and close rows of a bank limit the rate at which the bank can satisfy DRAM requests.

<sup>&</sup>lt;sup>1</sup>There are other elements of DRAM organization, such as *ranks* and *chips*; however, a description of these is not necessary to understand the performance impact of DRAM under frequency scaling.

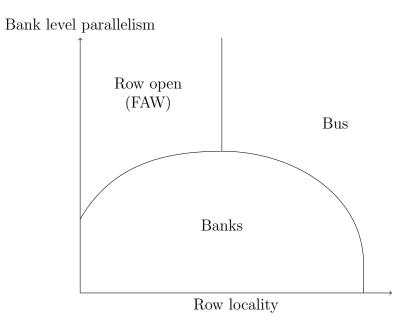

Figure 2.2: Qualitative relationship between row locality, bank level parallelism, and the dominant DRAM bandwidth bottleneck

3. *Bus bandwidth.* The time needed to transfer data over the bus and the overhead of changing the bus direction (read to write and vice versa) limit the rate at which the channel can satisfy DRAM requests.

Which of the three bandwidth constraints dominates depends on two parameters of the DRAM access stream: *row locality*, the number of row hits per row open, and *bank level parallelism*, the number of banks accessed simultaneously. Figure 2.2 shows the qualitative relationship between these two parameters and the dominant bandwidth bottleneck. The figure shows that

- the DRAM bus is the dominant DRAM bandwidth bottleneck when the DRAM access patterns exhibit large row buffer locality,

- the row open bandwidth is the dominant DRAM bandwidth bottleneck when the DRAM access patterns exhibit little row buffer locality but high bank level parallelism, and

• the DRAM banks are the dominant DRAM bandwidth bottleneck when both row buffer locality and bank level parallelism are relatively small.

As we show experimentally in Sections 3.3.1 and 4.1, a stream prefetcher (common in modern processors and described below) uncovers enough row locality to make the DRAM bus the major bandwidth bottleneck.

### 2.5 Stream Prefetching

Stream prefetchers are used in many commercial processors [6, 28, 47] and can greatly improve performance of memory intensive applications that stream through contiguous data arrays. Stream prefetchers do so by detecting memory access streams and generating memory requests for data the processor will request further down stream.

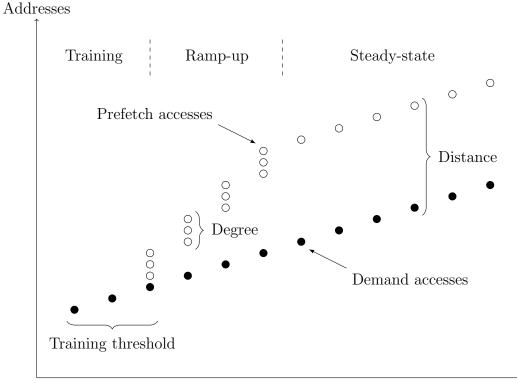

Figure 2.3 illustrates the high level operation of a stream prefetcher for a single stream of last level cache demand accesses to contiguous cache lines. The prefetcher handles a demand stream by progressing through three modes of operation:

- 1. *Training.* The prefetcher waits until the number of demand accesses fitting a stream access pattern crosses a *training threshold*.

- 2. *Ramp-up.* For every stream demand access, the prefetcher generates several prefetch requests (their number is the *degree*), building up the distance between the prefetch stream and the demand stream.

- 3. *Steady-state.* Once the distance between the prefetch stream and the demand stream reaches some threshold (the *distance*), the prefetcher tries to maintain that distance by sending out a single prefetch stream request for every demand stream request.

The prefetcher aims to generate prefetch requests early enough for them to bring data from DRAM before the corresponding demand requests are issued. Those prefetch

Demand stream accesses

Figure 2.3: Stream prefetcher operation

requests that are early enough are called *timely*. The stream prefetcher distance is usually set (either at design time or dynamically [79]) to be large enough to make all prefetch requests issued in steady-state mode timely.

## Chapter 3

## Uniprocessor

Big things have small beginnings, sir.

Mr. Dryden Lawrence of Arabia

In this chapter<sup>1</sup> we develop a DVFS performance predictor for the simplest processor configuration: the uniprocessor shown in Figure 3.1. We first describe the previously proposed predictors, *leading loads* and *stall time*, both based on a simple *linear* analytic model of performance. We then show experimentally that these predictors still have some room for improvement. Specifically, we show that

- the hardware mechanism used by the leading loads predictor to measure a key linear model parameter assumes a constant access latency memory system—an unrealistic assumption given the significant variation of DRAM request latencies in real DRAM systems, and

- the linear analytic model used by both predictors fails in the presence of prefetching because the model does not consider the performance impact of DRAM bandwidth saturation caused by prefetching.

<sup>&</sup>lt;sup>1</sup>An earlier version of this chapter was previously published in [60].

Figure 3.1: Uniprocessor

We address both of these shortcomings by

- designing a new hardware mechanism that accounts for variable DRAM request latencies when measuring the aforementioned linear model parameter, and

- developing a new *limited bandwidth* analytic model of performance under frequency scaling that does consider bandwidth saturation caused by prefetching.

Taken together, these improvements comprise our DVFS performance predictor for uniprocessors. According to this structure, we call this predictor CRIT+BW, since it is a sum of two parts: CRIT, the hardware mechanism for parameter measurement (which measures the length of a critical path through DRAM requests, hence the name "CRIT"), and BW, the limited bandwidth analytic model. We conclude the chapter by showing experimentally that CRIT+BW can make the processor more energy-efficient by guiding chip-level DVFS almost as well as an oracle predictor.

#### 3.1 Background

We first describe the basic linear model of processor performance under frequency scaling; we then describe *leading loads* and *stall time*, the two previously proposed DVFS performance predictors based on the linear model.

#### 3.1.1 Linear Model

The linear analytic model of performance under frequency scaling (*linear* DVFS performance model for short) arises from the observation that processor execution consists of two phases:

- 1. *compute*, that is on-chip computation, which continues until a burst of demand (instruction fetch or data load) DRAM accesses is generated, the processor runs out of ready instructions in the out-of-order instruction window, and stalls, and

- 2. *demand*, that is stalling while waiting for the generated demand DRAM accesses to complete.

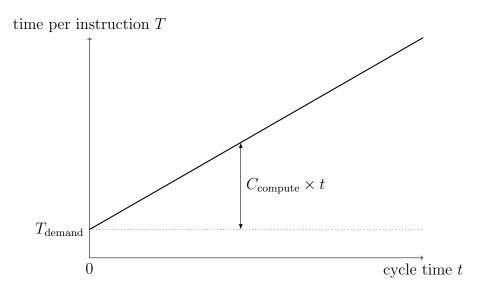

Figure 3.2: Linear DVFS performance model

This two-phase view of execution predicts a linear relationship between the average execution time per instruction T and chip cycle time t. To show this, we let

$$T = T_{\text{compute}} + T_{\text{demand}},$$

where  $T_{\text{compute}}$  denotes the average compute phase length per instruction and  $T_{\text{demand}}$ denotes the average demand phase length per instruction. As chip cycle time t changes due to DVFS, the average number of cycles  $C_{\text{compute}}$  the chip spends in compute phase per instruction stays constant; hence

$$T_{\text{compute}}(t) = C_{\text{compute}} \times t.$$

Meanwhile,  $T_{\text{demand}}$  remains constant for every frequency. Thus, given measurements of  $C_{\text{compute}}$  and  $T_{\text{demand}}$  at any cycle time, we can predict the average execution time per instruction at any other cycle time:

$$T(t) = C_{\text{compute}} \times t + T_{\text{demand}}.$$

(3.1)

This equation, illustrated in Figure 3.2, completely describes the linear DVFS performance model.

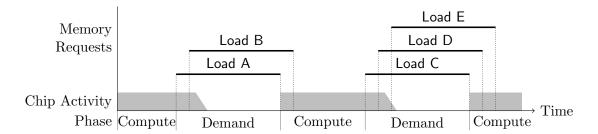

Figure 3.3: Abstract view of out-of-order execution with a constant access latency memory system assumed by leading loads

#### 3.1.2 Leading Loads

Leading loads [22, 37, 71]<sup>2</sup> is a previously proposed DVFS performance predictor based on the linear DVFS performance model and the assumption that the off-chip memory system has a constant access latency. Figure 3.3 shows the abstract view of execution implied by this assumption.

The major contribution of leading loads is its mechanism for measuring the two parameters of the linear model ( $T_{\text{demand}}$ , the average demand time per instruction, and  $C_{\text{compute}}$ , the average number of compute cycles per instruction) based on the constant access latency assumption.

We first start with measurement of  $T_{\text{demand}}$ . To measure  $T_{\text{demand}}$ , the leading loads predictor keeps a counter of total demand time and a counter of total instructions retired;  $T_{\text{demand}}$  is computed by dividing the former by the latter. Figure 3.3 shows that each demand request burst contributes the latency of a single demand request to the total demand time. The leading loads predictor measures that latency by measuring the length of the first (or "leading") demand request in the burst; since demand requests are usually data loads, this approach was named "leading loads" by Rountree et. al [71].

Once  $T_{\text{demand}}$  is measured, the other linear model parameter,  $C_{\text{compute}}$ , can be computed from  $T_{\text{demand}}$  and the easily measured execution time per instruction T.

$<sup>^{2}</sup>$ These three works propose very similar techniques. We use the name "leading loads" from Rountree et al. [71] for all three proposals.

Specifically, from Equation 3.1:

$$C_{\text{compute}} = \frac{T - T_{\text{demand}}}{t}.$$

(3.2)

The parameter measurement mechanism we just described and the linear DVFS performance model comprise the leading loads predictor. This predictor can be used to control chip-level frequency as described in Section 2.2.

#### 3.1.3 Stall Time

Like leading loads, the *stall time* [22, 37] DVFS predictor is the combination of the linear DVFS performance model and hardware mechanisms to measure its parameters. The key idea is simple: the time the processor spends unable to retire instructions due to an outstanding off-chip memory access should stay roughly constant as chip frequency is scaled (since this time depends largely on memory latency, which does not change with chip frequency). The stall time predictor uses this retirement stall time as a proxy for total demand time and computes  $T_{\text{demand}}$  by dividing the retirement stall time by the number of instructions retired. The  $C_{\text{compute}}$  parameter is computed exactly as in the leading loads predictor just described.

Unlike leading loads, the stall time predictor is not based on an abstract view of execution. Rather, the use of retirement stall time as a proxy for demand time is rooted in intuition.

### 3.2 CRIT: Accounting for Variable Access Latency Memory

Both leading loads and stall time DVFS performance predictors leave room for improvement; thus, we design an improved DVFS performance predictor we call CRIT (the reason for the name will soon become clear). Specifically, we note that

• leading loads is derived from an unrealistic abstract view of execution under a constant access latency memory system that fails to describe a more realistic variable access latency memory system, and

• stall time is rooted in intuition and is not based on an abstract view of execution, failing to provide a precise rationale for and hence confidence in its parameter measurement mechanism.

To overcome both of these shortcomings, we design our performance predictor from a more realistic abstract view of execution under a variable access latency memory system.

#### 3.2.1 Experimental Observations

We first show experimentally that the abstract view of execution used by leading loads breaks in the presence of a real DRAM system.

Table 3.1 shows results of a simulation experiment on SPEC 2006 benchmarks.<sup>3</sup> In this experiment, we compare the length of an average "leading load" DRAM request to the length of an average demand DRAM request. Recall that the leading loads predictor is based on a view of execution where the leading loads have the same latency as the other demand DRAM requests. Table 3.1 shows that this view is incorrect for a modern DRAM system. In fact, the average leading load latency is generally less than the average demand DRAM request latency; the ratio is as low as 63% for cactusADM. This discrepancy makes sense in a realistic DRAM system where, unlike a constant access latency memory system, requests actually contend for service. Specifically, a "leading load" DRAM request is less likely to suffer from contention since, as the oldest demand request, it is prioritized in DRAM scheduling over other requests, including demand requests from the same burst. Note also that this discrepancy shows up in benchmarks like **bwaves**, **leslie3d**, and **milc** which spend a large fraction of execution time waiting on memory (as seen in the last table column). For these benchmarks, inaccurate measurement of demand time per instruction  $T_{\text{demand}}$  is most problematic, since the fraction of the error in  $T_{\text{demand}}$

$<sup>^{3}</sup>$ Section 3.4 details the experimental methodology and simulated processor configuration.

| Benchmark                | Average<br>leading load<br>latency,<br>cycles | Average<br>DRAM request<br>latency,<br>cycles | Leading load<br>latency<br>relative to<br>average<br>demand request<br>latency, % | Demand<br>fraction of<br>execution time<br>as measured by<br>leading loads, % |

|--------------------------|-----------------------------------------------|-----------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| astar                    | 151                                           | 164                                           | 92                                                                                | 19                                                                            |

| bwaves                   | 138                                           | 188                                           | 73                                                                                | 37                                                                            |

| bzip2                    | 146                                           | 171                                           | 86                                                                                | 14                                                                            |

| cactusADM                | 182                                           | 290                                           | 63                                                                                | 25                                                                            |

| calculix                 | 135                                           | 135                                           | 100                                                                               | 9                                                                             |

| dealII                   | 106                                           | 108                                           | 98                                                                                | 6                                                                             |

| gamess                   | 99                                            | 112                                           | 89                                                                                | 0                                                                             |

| gcc                      | 121                                           | 126                                           | 96                                                                                | 9                                                                             |

| GemsFDTD                 | 181                                           | 215                                           | 84                                                                                | 45                                                                            |

| gobmk                    | 156                                           | 157                                           | 100                                                                               | 3                                                                             |

| gromacs                  | 101                                           | 109                                           | 92                                                                                | 4                                                                             |

| h264ref                  | 109                                           | 113                                           | 96                                                                                | 7                                                                             |

| hmmer                    | 141                                           | 145                                           | 97                                                                                | 0                                                                             |

| lbm                      | 241                                           | 252                                           | 96                                                                                | 48                                                                            |

| leslie3d                 | 118                                           | 161                                           | 73                                                                                | 44                                                                            |

| libquantum               | 104                                           | 109                                           | 95                                                                                | 65                                                                            |

| mcf                      | 190                                           | 211                                           | 90                                                                                | 62                                                                            |

| milc                     | 137                                           | 173                                           | 79                                                                                | 64                                                                            |

| namd                     | 93                                            | 97                                            | 96                                                                                | 1                                                                             |

| $\operatorname{omnetpp}$ | 161                                           | 173                                           | 93                                                                                | 58                                                                            |

| perlbench                | 153                                           | 162                                           | 95                                                                                | 3                                                                             |

| povray                   | 103                                           | 113                                           | 91                                                                                | 0                                                                             |

| sjeng                    | 175                                           | 188                                           | 93                                                                                | 5                                                                             |

| soplex                   | 112                                           | 132                                           | 85                                                                                | 61                                                                            |

| sphinx3                  | 105                                           | 118                                           | 89                                                                                | 50                                                                            |

| tonto                    | 92                                            | 104                                           | 89                                                                                | 1                                                                             |

| wrf                      | 123                                           | 173                                           | 71                                                                                | 19                                                                            |

| xalancbmk                | 161                                           | 173                                           | 93                                                                                | 15                                                                            |

| zeusmp                   | 168                                           | 179                                           | 94                                                                                | 44                                                                            |

Table 3.1: Applicability of leading loads

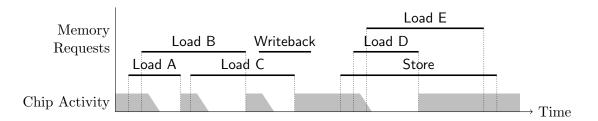

Figure 3.4: Abstract view of out-of-order processor execution with a variable latency memory system

measurement that propagates into the total predicted execution time per instruction  $T = T_{\text{demand}} + T_{\text{compute}}$  is proportional to  $T_{\text{demand}}$ .

Thus we conclude that the abstract view of processor execution used by the leading loads predictor does not apply to a processor with a realistic DRAM system.

#### 3.2.2 Variable Access Latency View of Processor Execution

This conclusion motivates the parameter measurement mechanism of our CRIT performance predictors; specifically, we design CRIT from a more realistic variable access latency view of processor execution.

Figure 3.4 illustrates the abstract view of processor execution when memory latency is allowed to vary. Note that the processor still eventually stalls under demand (instruction fetch and data load) memory requests, but the lengths of these requests are different.

The introduction of variable memory access latencies complicates the task of measuring the demand time per instruction  $T_{\text{demand}}$ . We must now calculate how execution time per instruction is affected by multiple demand requests with very different behaviors. Some of these requests are dependent and thus serialized (the first must return its data to the chip before the second one can be issued). Specifically, there are two kinds of dependence between requests:

1. *program dependence*, that is, when the address of the second request is computed from the data brought in by the first request, and

2. *resource dependence*, such as when the out-of-order instruction window is too small to simultaneously contain both instructions corresponding to the two memory requests.

Other requests, however, overlap freely.

To estimate  $T_{\text{demand}}$  in this case, we recognize that in the linear DVFS performance model,  $T_{\text{demand}}$  is the limit of execution time per instruction as chip frequency approaches infinity (or, equivalently, as chip cycle time approaches zero). In that hypothetical scenario, the execution time equals the length of the longest chain of dependent demand requests. We refer to this chain as the *critical path* through the demand requests.

To calculate the critical path, we must know which demand DRAM requests are dependent (and remain serialized at all frequencies) and which are not. We observe that independent demand requests almost never serialize; the processor generates independent requests as early as possible to overlap their latencies. Hence, we make the following assumption:

If two demand DRAM requests are serialized (the first one completes before the second one starts), the second one depends on the first one.

#### 3.2.3 Hardware Mechanism

We now describe CRIT, the hardware mechanism that uses the above assumption to estimate the critical path through load and fetch memory requests. CRIT maintains one global critical path counter  $P_{\text{global}}$  and, for each outstanding DRAM request *i*, a critical path timestamp  $P_i$ . Initially, the counter and timestamps are set to zero. When a request *i* enters the memory controller, the mechanism copies  $P_{\text{global}}$  into  $P_i$ . After some time  $\Delta T$  the request completes its data transfer over the DRAM bus. At that time, if the request was generated by an instruction fetch or a data load, CRIT sets  $P_{\text{global}} = \max(P_{\text{global}}, P_i + \Delta T)$ . As such, after each fetch or load request *i*,

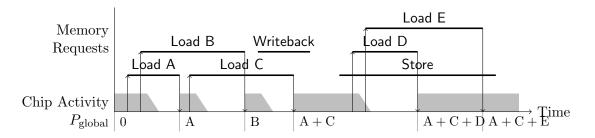

Figure 3.5: Critical path calculation example

CRIT updates  $P_{\text{global}}$  if request *i* is at the end of the new longest path through the memory requests.

Figure 3.5 illustrates how the mechanism works. We explain the example step by step:

- 1. At the beginning of the example,  $P_{\text{global}}$  is zero and the chip is in a compute phase.

- Eventually, the chip incurs two load misses in the last level cache and generates two memory requests, labeled Load A and Load B. These misses make copies of P<sub>global</sub>, which is still zero at that time.

- 3. Load A completes and returns data to the chip. Our mechanism adds the request's latency, denoted as A, to the request's copy of  $P_{\text{global}}$ . The sum represents the length of the critical path through Load A. Since the sum is greater than  $P_{\text{global}}$ , which is still zero at that time, the mechanism sets  $P_{\text{global}}$  to A.

- 4. Load A's data triggers more instructions in the chip, which generate the Load C request. Load C makes a copy of P<sub>global</sub>, which now has the value A (the latency of Load A). Initializing the critical path timestamp of Load C with the value A captures the dependence between Load A and Load C: the latency of Load C will eventually be added to that of Load A.

- 5. Load B completes and ends up with B as its version of the critical path length. Since B is greater than A, B replaces A as the length of the global critical path.

- 6. Load C completes and computes its version of the critical path length as A + C. Again, since A + C > B, CRIT sets P<sub>global</sub> to A + C. Note that A + C is indeed the length of the critical path through Load A, Load B, and Load C.

- 7. We ignore the writeback and the store because they do not cause a processor stall.<sup>4</sup>

- 8. Finally, the chip generates requests Load D and Load E, which add their latencies to A + C and eventually result in  $P_{\text{global}} = A + C + E$ .

We can easily verify the example by tracing the longest path between dependent loads, which indeed turns out to be the path through Load A, Load C, and Load E. Note that, in this example, leading loads would incorrectly estimate  $T_{\text{demand}}$  as A + C + D.

### 3.2.4 Summary

We have just described our hardware mechanism for measuring demand time per instruction  $T_{\text{demand}}$ , which is a workload characteristic and a parameter of the linear analytic model. The other parameter of the model,  $C_{\text{compute}}$  can be computed using Equation 3.2 as done by both leading loads and stall time predictors. Our mechanisms to measure/compute these parameters together with the linear analytic model comprise our CRIT performance predictor. We defer its evaluation until Section 3.5.1.

# **3.3 BW: Accounting for DRAM Bandwidth Saturation**

Having proposed CRIT, a new parameter measurement mechanism for the linear analytic model, we now turn our attention to the linear model itself. In this section, we show experimentally that the linear model does not account for the performance impact of DRAM bandwidth saturation caused by prefetching. We then fix

<sup>&</sup>lt;sup>4</sup>Stores may actually cause processor stalls due to insufficient store buffer capacity or memory consistency constraints [88]. CRIT can be easily modified to account for this behavior by treating such stalling stores as demands.

this problem and develop a new limited bandwidth analytic model on top of the linear model by taking into account bandwidth saturation. We also augment CRIT to work with this new analytic model and design hardware to measure an extra parameter needed by the new model. All together, these hardware mechanisms and the new limited bandwidth model comprise CRIT+BW, our DVFS performance predictor for uniprocessors.

#### 3.3.1 Experimental Observations

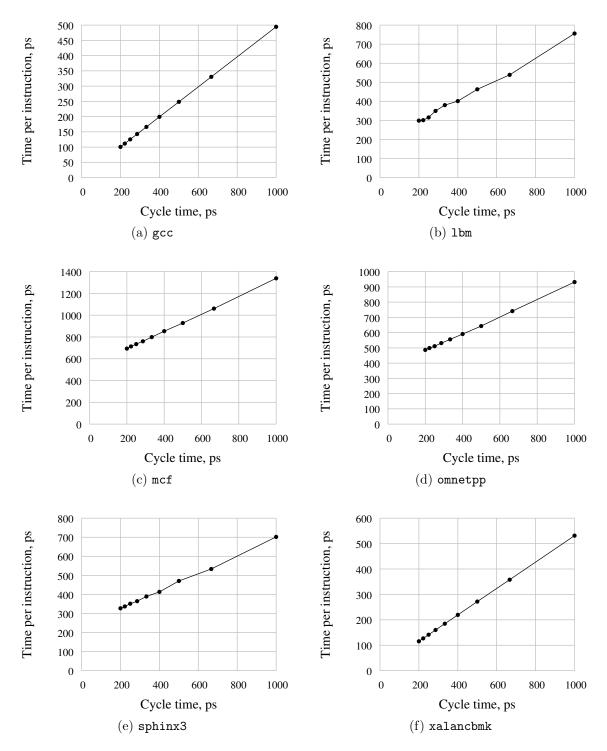

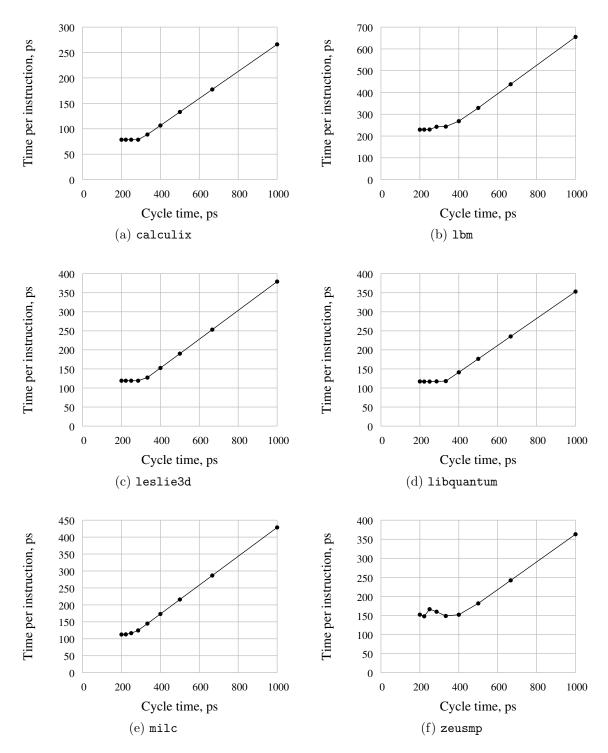

Figure 3.6 shows how performance of six SPEC 2006 benchmarks scales under frequency scaling when prefetching is off. The six plots were obtained by simulating a 100K instruction interval of each benchmark at a range of frequencies from 1 GHz to 5 GHz. Note that most plots, except the one for 1bm, match the linear analytic model. Comparing these plots to Figure 3.2, we see that some benchmarks (like gcc and xalancbmk) exhibit low demand time per instruction  $T_{demand}$ , spending most execution time in on-chip computation even at 5 GHz. Others (like mcf and omnetpp) exhibit high  $T_{demand}$  and spend most of their execution time at 5 GHz stalled for demand DRAM requests. Both kinds, however, are well described by the linear analytic model. The apparent exception 1bm follows the linear model for most of the frequency range, but seems to taper off at 5 GHz. We shall soon see the reason for this anomaly.

Figure 3.6 shows how performance of six SPEC 2006 benchmarks scales under frequency scaling in the presence of a stream prefetcher (Section 2.5) over 100K instruction intervals where these benchmarks exhibit streaming data access patterns. Note that none of the plots match the linear model: instead of decreasing linearly with chip cycle time, the time per instruction saturates at some point.

The linear model fails to describe processor performance in these examples due to the special nature of prefetching. Unlike demand DRAM requests, a prefetch DRAM request is issued in advance of the instruction that consumes the request's data. Recall from Section 2.5 that a prefetch request is *timely* if it fills the cache before

Figure 3.6: Linear model applicability with prefetching off: performance impact of frequency scaling on 100K instruction intervals of SPEC 2006 benchmarks

Figure 3.7: Linear model failure with prefetching on: performance impact of frequency scaling on 100K instruction intervals of prefetcher-friendly SPEC 2006 benchmarks

the consumer instruction accesses the cache. Timely prefetches do not cause processor stalls; hence, their latencies do not affect execution time. Without stalls, however, the processor may generate prefetch requests at a high rate, exposing another performance limiter: the rate at which the DRAM system can satisfy DRAM requests—the DRAM bandwidth.

Table 3.2 provides more insight into DRAM bandwidth saturation. Recall from Section 2.4 that modern DRAM has three potential bandwidth bottlenecks: bus, banks, and row open rate (determined by the "four activate window", or FAW, timing constraint). For each SPEC 2006 benchmark, the table lists the fraction of time each of these potential bandwidth bottlenecks is more than 90% utilized. The left side of the table shows this data for simulation experiments with prefetching off; the right side shows results with a stream prefetcher enabled. Note that bandwidth saturation of any potential bottleneck is rare when prefetching is off (with the exception of 1bm which explains its anomalous behavior seen earlier). On the other hand, in the presence of a stream prefetcher, the DRAM bus is not only often saturated but is also the only significant DRAM bandwidth bottleneck.

The simulation results in Table 3.2 clearly show that the DRAM bus is the major DRAM bandwidth bottleneck; we now explain why. To become bandwidth-bound, a workload must generate DRAM requests at a high rate. DRAM requests can be generated at a high rate if they are independent; that is, the data brought in by one is not needed to generate the addresses of the others. In contrast, dependent requests (for example, those generated during linked data structure traversals) cannot be generated at a high rate, since the processor must wait for a long latency DRAM request to complete before generating the dependent request. The independence of DRAM requests needed to saturate DRAM bandwidth is a hallmark of streaming workloads, that is workloads that access data by iterating over arrays (either consecutively or using a short stride). An extreme example is 1bm, which simultaneously streams over ten arrays (which are actually subarrays within two three-dimensional arrays). The memory layout of such arrays (e.g., column-major or row-major) is usually cho-

|                         |                 | is more than 90% utilized, in $\%$ |     |                |       |     |  |  |

|-------------------------|-----------------|------------------------------------|-----|----------------|-------|-----|--|--|

|                         | Prefetching off |                                    |     | Prefetching on |       |     |  |  |

| Benchmark               | Bus             | Banks                              | FAW | Bus            | Banks | FAW |  |  |

| astar                   | 2.3             | 0.0                                | 0.0 | 2.7            | 0.0   | 0.0 |  |  |

| bwaves                  | 0.3             | 4.5                                | 0.0 | 88.9           | 0.3   | 0.0 |  |  |

| bzip2                   | 6.5             | 0.1                                | 0.0 | 12.0           | 0.0   | 0.0 |  |  |

| cactusADM               | 8.0             | 0.7                                | 0.0 | 7.9            | 0.6   | 0.0 |  |  |

| calculix                | 7.1             | 0.0                                | 0.0 | 7.9            | 0.0   | 0.0 |  |  |

| dealII                  | 0.2             | 0.0                                | 0.0 | 0.4            | 0.0   | 0.0 |  |  |

| gamess                  | 0.0             | 0.0                                | 0.0 | 0.0            | 0.0   | 0.0 |  |  |

| gcc                     | 0.3             | 0.0                                | 0.0 | 0.8            | 0.0   | 0.0 |  |  |

| GemsFDTD                | 6.1             | 0.2                                | 0.0 | 48.4           | 0.2   | 0.0 |  |  |

| $\operatorname{gobm} k$ | 0.1             | 0.0                                | 0.0 | 0.2            | 0.0   | 0.0 |  |  |

| gromacs                 | 0.2             | 0.0                                | 0.0 | 0.2            | 0.0   | 0.0 |  |  |

| h264ref                 | 0.8             | 0.0                                | 0.0 | 2.1            | 0.0   | 0.0 |  |  |

| hmmer                   | 0.0             | 0.0                                | 0.0 | 0.1            | 0.0   | 0.0 |  |  |

| lbm                     | 94.9            | 0.1                                | 0.0 | 99.3           | 0.0   | 0.0 |  |  |

| leslie3d                | 1.8             | 5.4                                | 0.0 | 43.4           | 0.1   | 0.0 |  |  |

| libquantum              | 17.4            | 0.7                                | 0.0 | 80.9           | 0.0   | 0.0 |  |  |

| $\mathrm{mcf}$          | 0.1             | 0.0                                | 0.0 | 0.2            | 0.0   | 0.0 |  |  |

| milc                    | 18.0            | 2.1                                | 0.0 | 39.7           | 0.0   | 0.0 |  |  |

| namd                    | 0.1             | 0.0                                | 0.0 | 0.1            | 0.0   | 0.0 |  |  |

| omnetpp                 | 0.3             | 0.0                                | 0.0 | 0.9            | 0.0   | 0.0 |  |  |

| perlbench               | 0.5             | 0.0                                | 0.0 | 0.6            | 0.0   | 0.0 |  |  |

| povray                  | 0.0             | 0.0                                | 0.0 | 0.0            | 0.0   | 0.0 |  |  |

| sjeng                   | 0.0             | 0.0                                | 0.0 | 0.0            | 0.0   | 0.0 |  |  |

| soplex                  | 2.7             | 1.7                                | 0.0 | 71.7           | 1.4   | 0.0 |  |  |

| sphinx3                 | 1.0             | 0.3                                | 0.0 | 36.7           | 0.2   | 0.0 |  |  |

| tonto                   | 0.2             | 0.0                                | 0.0 | 0.0            | 0.0   | 0.0 |  |  |

| wrf                     | 1.3             | 1.4                                | 0.0 | 7.4            | 0.3   | 0.0 |  |  |

| xalancbmk               | 0.2             | 0.0                                | 0.0 | 1.4            | 0.0   | 0.0 |  |  |

| zeusmp                  | 0.4             | 0.1                                | 0.0 | 1.2            | 0.0   | 0.0 |  |  |

| Fraction o | f time each | potential               | DRAM      | bandwidth  | bottleneck |

|------------|-------------|-------------------------|-----------|------------|------------|

|            | is more     | e than $90^{\circ}_{2}$ | % utilize | d, in $\%$ |            |

Table 3.2: Bandwidth bottlenecks in the uniprocessor

sen with these streaming DRAM access patterns in mind in order to exploit row locality, making the DRAM bus the most likely bandwidth bottleneck even without prefetching. Once on, the stream prefetcher further speeds up streaming workloads and uncovers even more row locality; therefore, streaming workloads become even more likely to saturate the DRAM bus.<sup>5</sup>

Now that we uncovered the performance limiting effect of DRAM bandwidth saturation and observed the DRAM bus to be the dominant DRAM bandwidth bottleneck, we are ready to develop a new DVFS performance predictor that takes these observations into account. We start with a new analytic model and then develop hardware mechanisms to measure its parameters.

## 3.3.2 Limited Bandwidth Analytic Model

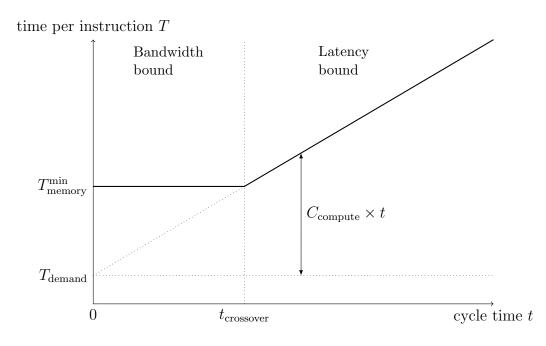

We now describe the limited bandwidth analytic model of uniprocessor performance under frequency scaling, illustrated in Figure 3.8, that takes into account the performance limiting effect of finite memory bandwidth exposed by prefetching. This model splits the chip frequency range into two parts:

- 1. the low frequency range where the DRAM system can service memory requests at a higher rate than the chip generates them, and

- 2. the high frequency range where the DRAM system cannot service memory requests at the rate they are generated.

In the low frequency range, shown to the right of  $t_{\text{crossover}}$  in Figure 3.8, the prefetcher runs ahead of the demand stream because the DRAM system can satisfy prefetch requests at the rate the prefetcher generates them. Therefore, DRAM bandwidth is not a performance bottleneck in this case. In fact, in this case the time per

<sup>&</sup>lt;sup>5</sup>Irregular access prefetchers [12, 32, 35, 89] (yet to be used in commercial processors) may also saturate DRAM bandwidth; however, unlike stream prefetchers, these prefetchers generate requests mapped to different DRAM rows. In this high bandwidth yet low row locality scenario, the DRAM bus may no longer be the dominant bandwidth bottleneck.

Figure 3.8: Limited bandwidth DVFS performance model

instruction T is modeled by the original linear model, with only the non-prefetchable demand memory requests contributing to the demand time per instruction  $T_{\text{demand}}$ .

In the high frequency range, shown to the left of  $t_{\text{crossover}}$  in Figure 3.8, the prefetcher fails to run ahead of the demand stream due to insufficient DRAM bandwidth. As the demand stream catches up to the prefetches, some demand requests stall the processor as they demand data that the prefetch requests have not yet brought into the cache. In this high frequency range the execution time per instruction is determined solely by  $T_{\text{memory}}^{\min}$ : the minimum average time per instruction that the DRAM system needs to satisfy all of the memory requests. Therefore, time per instruction T does not depend on chip frequency in this case.

The limited bandwidth DVFS performance model shown in Figure 3.8 has three parameters:

- 1. the demand time per instruction  $T_{\text{demand}}$ ,

- 2. the number of compute cycles per instruction  $C_{\text{compute}}$ , and

3. the minimum memory time per instruction  $T_{\text{memory}}^{\min}$ .

Given the values of these parameters, we can estimate the execution time per instruction T at any other cycle time t as follows:

$$T(t) = \max\left(T_{\text{memory}}^{\min}, \ C_{\text{compute}} \times t + T_{\text{demand}}\right).$$

(3.3)

# 3.3.2.1 Approximations Behind $T_{\text{memory}}^{\min}$

In this section, we address the implicit approximations related to the  $T_{\text{memory}}^{\min}$  workload characteristic used by the limited bandwidth model. Specifically, our notion that the minimum memory time per instruction  $T_{\text{memory}}^{\min}$  is a workload characteristic that stays constant across chip frequencies relies on two approximations:

- 1. The average number of DRAM requests per instruction (both demands and prefetches) remains constant across chip frequencies. This approximation is generally accurate in the absence of prefetching; however, with prefetching on this approximation is less accurate. Specifically, modern prefetchers may adapt their aggressiveness based on bandwidth consumption, which may change with chip frequency, causing the average number of DRAM requests per instruction to also vary with chip frequency.

- 2. The DRAM scheduler efficiency remains the same across chip frequencies. In particular, we approximate that the average overhead of switching the DRAM bus direction per DRAM request remains the same across chip frequencies.

#### 3.3.3 Parameter Measurement

We now develop the hardware mechanisms for measuring the three parameters of the limited bandwidth analytic model. These mechanisms are complicated by the fact that the analytic model allows for two modes of processor operation: latencybound and bandwidth-bound. Therefore we have to ensure our mechanisms work in both modes.

## 3.3.3.1 Demand Time per Instruction T<sub>demand</sub>

In Section 3.2 we have already developed the CRIT hardware mechanism to measure demand time per instruction  $T_{\text{demand}}$  for the linear analytic model; however, it requires a slight alteration to work with our new limited bandwidth analytic model.

In fact, CRIT does not measure  $T_{\text{demand}}$  correctly in the bandwidth-bound mode of operation. Like leading loads and stall time, CRIT is based on the assumption that the number of demand DRAM requests per instruction and their latencies remain (on average) the same across chip frequencies. Prefetching in bandwidth-bound mode violates this assumption.

This effect concerns prefetch DRAM requests that are timely when the core is latency-bound (recall from Section 2.5 that *timely* prefetch requests bring their data into the cache before a demand request for that data is generated). Specifically, DRAM bandwidth saturation at higher chip frequencies increases DRAM request service time, causing some of these timely prefetch requests to become untimely. In fact, limited bandwidth may force the prefetcher to drop some prefetch requests altogether due to the prefetch queue and MSHRs being full, causing extra demand requests for the would be prefetched data. As a result, when bandwidth-bound, a core appears to exhibit more demand time per instruction than when latency-bound (due to a higher number of demand requests and untimely prefetch requests than in latency-bound mode). This effect is undesirable because for a DVFS performance predictor to be accurate all workload characteristics must stay the same across core frequencies.