# Department of Electrical and Computer Engineering The University of Texas at Austin

EE 360N, Fall 2003 Yale Patt, Instructor Santhosh Srinath, Danny Lynch, TAs Exam 1, October 20, 2003

| Name:                  |

|------------------------|

|                        |

|                        |

| Problem 1 (20 points): |

| Problem 2 (20 points): |

| Problem 3 (20 points): |

| Problem 4 (20 points): |

| Problem 5 (20 points): |

| Total (100 points):    |

Note: Please be sure that your answers to all questions (and all supporting work that is required) are contained in the space provided.

Note: Please be sure your name is recorded on each sheet of the exam.

**GOOD LUCK!**

| Name:                                   |                                                                                                                                                                                                                                    |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Problem                                 | 1 (20 points):                                                                                                                                                                                                                     |

|                                         | points): All of the following are important considerations that every manufacturer deals with in the design t microprocessor. Circle all those that are provided to increase performance of the executing program:                 |

|                                         | compatibility                                                                                                                                                                                                                      |

|                                         | unaligned accesses                                                                                                                                                                                                                 |

|                                         | memory interleaving                                                                                                                                                                                                                |

|                                         | a TLB                                                                                                                                                                                                                              |

|                                         | virtual memory                                                                                                                                                                                                                     |

| The page >k =k <k< td=""><td></td></k<> |                                                                                                                                                                                                                                    |

| Part c (5                               | points): Two structures already discussed in class that can be classified as content addressable memories are                                                                                                                      |

|                                         | o points): Since the microarchitect is able to use all the internal structures of the microarchitecture to his/her nce, what is the first thing the hardware has to do in dealing with an exception or interrupt? Ten words or se. |

| Name:                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Problem 3 (20 points):                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| We wish to add virtual memory to the LC-3b. What we have been calling addresses thus far will now be called virtual addresses. That is, VA space is $2^{16}$ bytes. We wish to specify our memory management system in a way similar to the VAX, which we have studied. However, we will only designate 1/8 of the VA space as system space, specifically the last 1/8 of the VA space (locations xE000 to xFFFF). Assume PA space is $2^{10}$ bytes, and page size is $2^6$ bytes. |

| Page tables are formed in the same way we did for the VAX, with each PTE containing 3 access control bits, a reference bit (unlike the VAX), and other bits that make sense.                                                                                                                                                                                                                                                                                                        |

| The P0BR is xE040. The SBR is 0x020.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Part a (3 points) What is the appropriate size for a PTE?                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Part b (5 points) What is the maximum size of the system page table?                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Part c (6 points) The VA of Y is x0082. What is the VA of the PTE of the page containing Y?                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Part d (6 points) The VA of Z is xE100. What is the PA of the PTE of the page containing Z?                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Name: |

|-------|

|-------|

# Problem 4 (20 points):

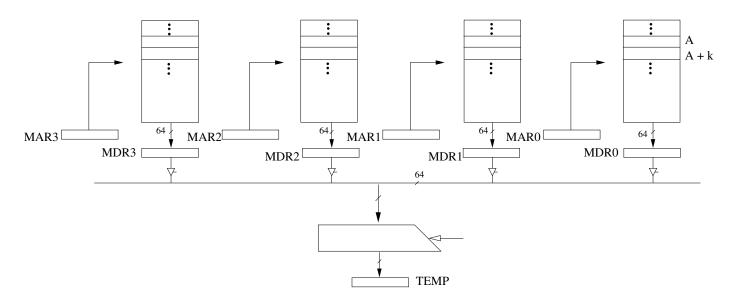

A four-way interleaved, byte-addressable memory is shown in the figure. We can load one MAR each successive cycle if necessary. It takes ten cycles after the MAR is loaded, to load the corresponding MDR with the contents of the memory locations in its respective memory array. It takes an additional cycle to gate MDR onto the bus and load its contents into TEMP. The processor supports unaligned memory accesses. LDBIG loads 64 bits from memory into a register.

Part a (3 points) Note the address labeled A+k. What is k?

**Part c** (4 points) Consider LDBIG R3, B, where B is a multiple of 8. How many cycles are required to get the contents of B into TEMP, after the appropriate MAR is loaded with B.

| Name:                                                                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Problem 4 continued:                                                                                                                                         |

| Part d (5 points) Redo Part c if B is decimal 8002.                                                                                                          |

|                                                                                                                                                              |

|                                                                                                                                                              |

|                                                                                                                                                              |

| <b>Part e</b> (5 points) In Part d, which LD_ENABLE signals of TEMP are asserted in the cycle where TEMP is loaded with its final value (the contents of B). |

|                                                                                                                                                              |

|                                                                                                                                                              |

|                                                                                                                                                              |

| Name: |  |

|-------|--|

|       |  |

|       |  |

# Problem 5 (20 points):

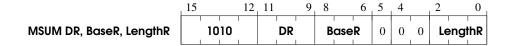

We wish to add to the LC-3b the new instruction MSUM, which adds the contents of k consecutive memory locations, and stores the result in one of the general purpose registers. The condition codes will be set according to whether the result is negative, zero, or positive. We will use the unused opcode 1010 for this purpose. The format of the instruction will be

where the address of the first location to be added is in BaseR, and the number of locations to be added is in LengthR.

If LengthR is initially 0, MSUM stores 0 in DR.

There is no requirement that the contents of BaseR or LengthR remain unchanged at the end of this instruction's execution.

# Example:

After the instruction MSUM R1,R2,R3 is executed, where R2 contains x4000, R3 contains #5, and memory is as shown below, R1 will contain the value #8, and condition P will be set.

| x4000 | 1 |

|-------|---|

| x4001 | 2 |

| x4002 | 0 |

| x4003 | 3 |

| x4004 | 2 |

Name:\_\_\_\_

# Problem 5 continued:

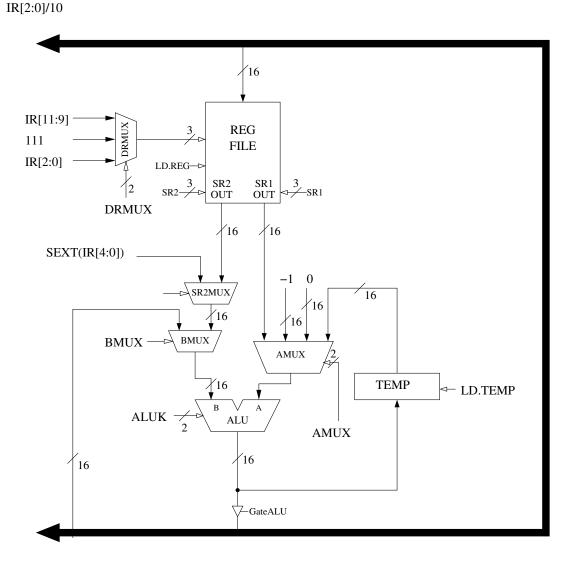

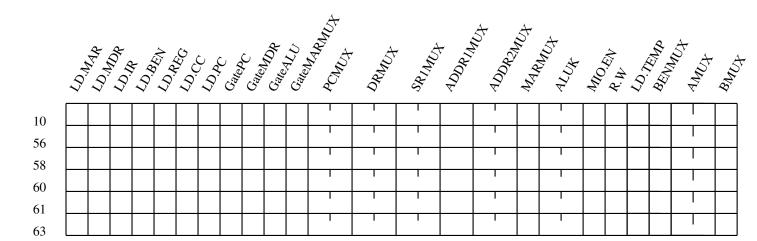

To implement MSUM, we have chosen to add the following to the LC-3b data path:

- 1. A new TEMP register, which is sourced from the output of the ALU. This requires a new control signal, LD\_TEMP.

- 2. A four-input MUX to the A input of the ALU. This requires a new control field, AMUX, specified as follows: SR1/00, the SR1 source from the original data path,

MINUS1/01, a constant -1,

ZERO/10, a constant 0,

TEMP/11, the contents of the new TEMP register.

- 3. A two-input MUX to the B input of the ALU. This requires a new control signal, BMUX, specified as follows: SR2MUX/0, the SR2MUX output from the original data path, BUS/1, the contents on the bus.

- 4. A third input (IR[2:0]) to the DRMUX. This requires extending the DRMUX control field to 2 bits: IR[11:9]/00, 111/01, IR[2:0]/10

Name:

Problem 5 continued:

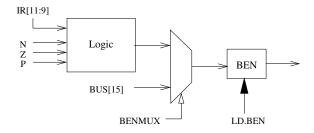

5. We have also added a BENMUX at the input of the BEN register, as shown. This requires a new control signal, BENMUX, specified as follows:

Logic/0 BUS[15]/1

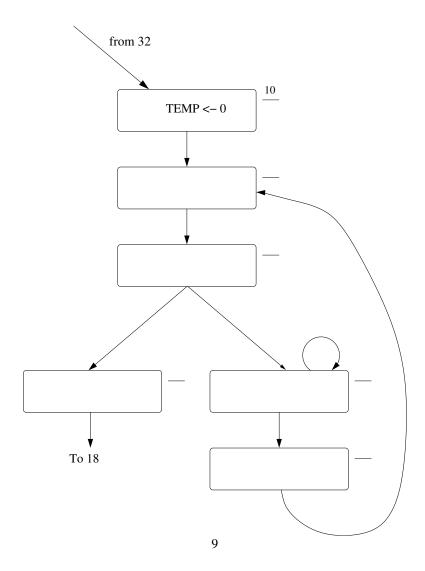

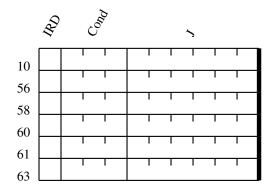

**Part a.** (12 points): We have provided the skeleton of the augmented LC-3b state machine for you to implement MSUM. Using the notation we have adopted for the LC-3b, show what happens in every state. Specify the assignment (i.e, the state number) of each state you use. The five states should be selected from the set 56, 58, 60, 61, 63. Note that state 10, the first state after decode, has both been assigned its state number (i.e., "10") and also has been filled in.

Name:

Problem 5 continued:

**Part b.** (8 points): Specify the control signals required (for both data path control and microsequencer control) to implement each state. Note that we have added control signals corresponding to our changes in the data path.

|                    | 15 | 14 | 13 | 12 |   | 10  | 9  | 8 | 7   | 6   | 5     | 4      | 3    | 2       | 1          | 0 |

|--------------------|----|----|----|----|---|-----|----|---|-----|-----|-------|--------|------|---------|------------|---|

| ADD⁺               |    |    | 01 |    |   | DR  |    |   | SR1 |     | 0     |        | 0    |         | SR2        |   |

| ADD <sup>⁺</sup>   |    | 00 | 01 |    |   | DR  |    |   | SR1 |     | 1     |        |      | nm      |            |   |

| AND <sup>⁺</sup>   |    | 01 | 01 |    |   | DR  |    |   | SR1 |     | 0     | 0      | 0    |         | SR2        |   |

| AND⁺               |    | 01 | 01 |    |   | DR  |    |   | SR1 |     | 1     |        |      | nm<br>' | 5          |   |

| BR                 |    | 00 |    |    | n | z   | р  |   |     |     | PC    |        |      | ı       |            |   |

| JMP                |    |    | 00 |    |   | 000 |    | В | ase | R   |       |        | 000  | 000     | )<br> <br> |   |

| JSR                | 1  | 01 | 00 |    | 1 |     |    |   | I   | PCo | offse | et 1 1 |      | ı       |            |   |

| JSRR               |    | 01 | 00 |    | 0 | 0   |    |   | ase |     |       |        | 000  | 000     | )<br> <br> |   |

| LDB <sup>+</sup>   |    | 00 | 10 |    |   | DR  |    | В | ase | R   |       |        | off  | set     | 5<br>1     |   |

| LDW *              |    | 01 | 10 |    |   | DR  |    |   | ase |     |       |        | offs | et6     |            |   |

| LEA <sup>+</sup>   |    | 11 | 10 |    |   | DR  |    |   |     |     | PC    | offs   | et9  |         |            |   |

| $NOT^{^{t}}$       |    | 10 | 01 |    |   | DR  |    |   | SR  |     | 1     |        | 1    | 111     |            |   |

| RET                |    | 11 | 00 |    |   | 000 |    |   | 111 |     |       | (      | 000  | 000     | )          |   |

| RTI                |    | 10 | 00 |    |   |     |    | ( |     | 000 | 000   | 000    | )    |         |            |   |

| LSHF *             |    | 11 | 01 |    |   | DR  |    |   | SR  | ı   |       | 0      | 0    | mo      | unt        | 4 |

| RSHFL <sup>⁺</sup> | 1  | 11 | 01 |    |   | DR  |    |   | SR  |     | 0     | 1      | o    | ı       | unt        | 4 |

| RSHFA <sup>†</sup> |    | 11 |    |    |   | DR  |    |   | SR  |     | 1     | 1      | o    | ımo     | unt        | 4 |

| STB                | 1  | 00 | 11 |    |   | SR  |    | В | ase | R   |       |        | off  | set     | 5<br>1     |   |

| STW                | 1  | 01 | 11 |    |   | SR  |    | В | ase | R   |       |        | offs | et6     |            |   |

| TRAP               |    | 11 | 11 |    |   | 00  | 00 |   |     |     | tre   | apv    | ec   | †8      |            |   |

| $XOR^{^{\dagger}}$ | 1  | 10 | 01 |    |   | DR  |    | , | SR1 |     | 0     | 0      | 0    |         | SR2        |   |

| XOR <sup>⁺</sup>   | ī  | 10 | 01 |    |   | DR  |    |   | SR  |     | 1     |        | i    | mm      | 5          |   |

| not used           |    | 10 | 10 |    |   |     |    |   |     |     |       |        |      |         |            |   |

| not used           | 1  | 10 |    |    |   |     |    |   |     |     |       |        |      | ı       |            |   |

<sup>+</sup> indicates instructions that modify condition codes.

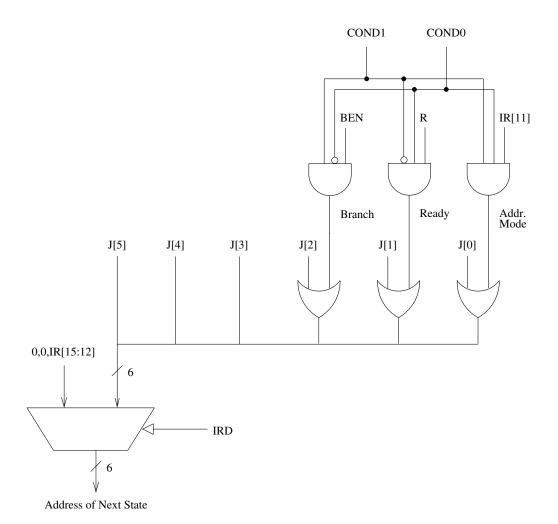

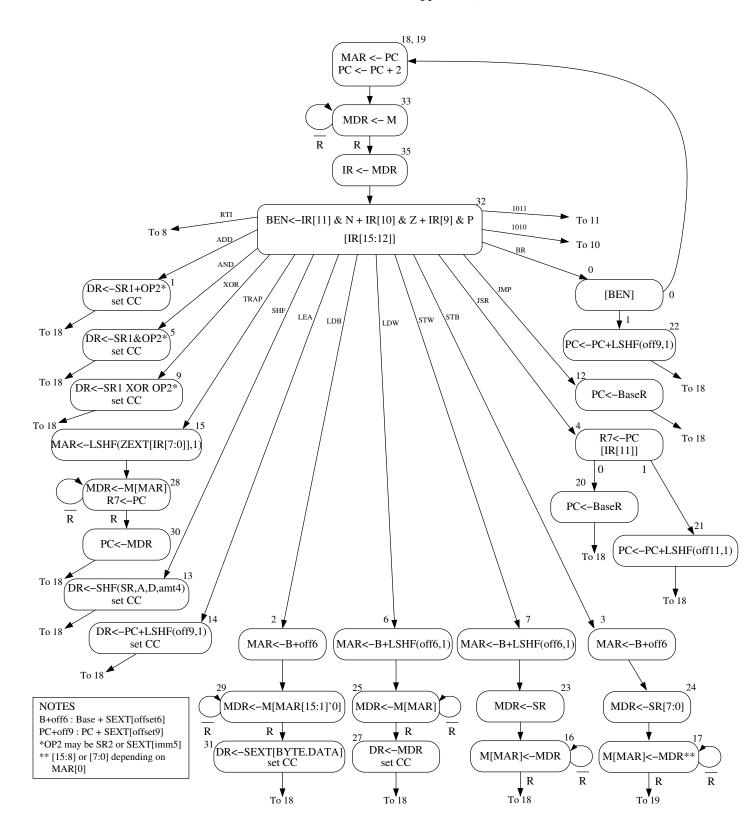

# A state machine for the LC-3b (from Appendix C)

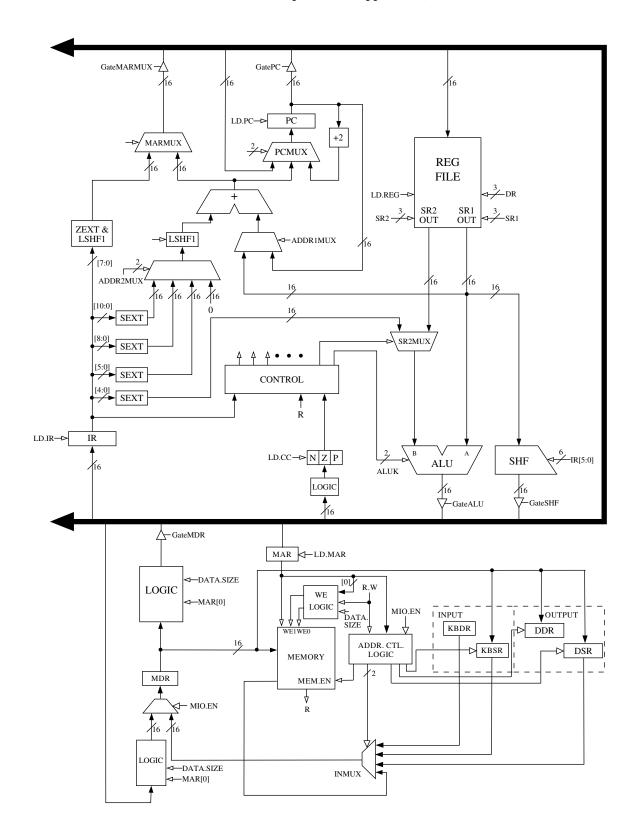

The LC-3b datapath (from Appendix C)