# Department of Electrical and Computer Engineering The University of Texas at Austin

EE 360N, Fall 2005 Yale Patt, Instructor Aater Suleman, Linda Bigelow, Jose Joao, Veynu Narasiman, TAs Exam 1, October 19, 2005

| Name: | Solution               |   |    |  |

|-------|------------------------|---|----|--|

|       |                        | 2 | u, |  |

|       | Problem 1 (20 points): | _ |    |  |

|       | Problem 2 (20 points): | _ |    |  |

|       | Problem 3 (20 points): | _ |    |  |

|       | Problem 4 (20 points): | _ |    |  |

|       | Problem 5 (20 points): | _ |    |  |

|       | Total (100 points):    |   |    |  |

Note: Please be sure that your answers to all questions (and all supporting work that is required) are contained in the space provided.

Note: Please be sure your name is recorded on each sheet of the exam.

GOOD LUCK!

| Name:                      |                      | _                       |                          |                          |

|----------------------------|----------------------|-------------------------|--------------------------|--------------------------|

| Problem 1 (20 points)      |                      |                         |                          |                          |

| Part a (4 points): The VAI | X has an instruction | INSQUE ptr1, ptr2 wl    | nich causes the node poi | inted to by ptrl to be   |

| data tup                   | 2                    | supported in the        |                          | loubly liliked list is a |

| L cocia JF                 |                      |                         |                          |                          |

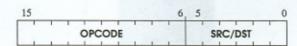

| Part b (5 points): The PDP | 11 had savaral two   | onerand instructions wi | ish the format           |                          |

| rare b (3 points): The PDF |                      | 6, 5                    | o o                      |                          |

|                            | OPCODE               |                         | RC2/DST                  |                          |

one-operand instructions with the format

and zero-operand instructions with the format

The ADD instruction had opcode 0110. The prefix property guaranteed

No other opcode starts with 0110

| Name: |   |

|-------|---|

|       | _ |

#### Problem 1 continued

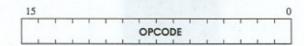

Part c (6 points): The virtual memory management system is called into play on every memory access instruction. In addition to translation, the right to access the information in the memory location is determined. The logic is as follows:

Identify the three elements that are input to the combinational logic required to make the yes/no access decision.

Part d (5 points): A page table has a base register and a length (aka limit) register. The purpose of the length register is

To specify the size of the image in pages

What would happen if we did not have one?

We could access memory beyond the page table, thinking it was aPTE, and compute the PA using bogus information

Name:\_\_\_\_\_

#### Problem 2 (20 points)

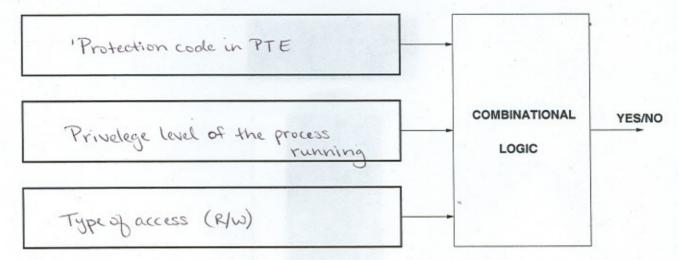

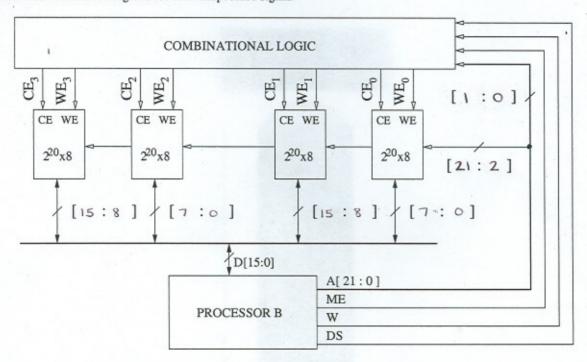

Part a (10 points): You are given four 1 MB, 8-bit wide, DRAM chips to build a 4 MB, 2-way interleaved, word-addressable main memory of a little-endian computer. Specify the bit fields indicated in the shaded regions for each unspecified signal.

Write the logic equations  $CE_0$ ,  $WE_0$ , ...,  $CE_3$ ,  $WE_3$  in terms of the inputs shown. Do not use more inputs than required to specify each output.

$$WE_1 =$$

no byte-on-bus bits because it is word addressable and-thebus is 16 bits

| Name: |  |  |

|-------|--|--|

|       |  |  |

#### Problem 2 continued:

Part b (10 points): Suppose the memory system of Part a was changed to byte-addressable. That is, the four 1 MB, 8-bit wide DRAM chips form a 4 MB, 2-way interleaved, byte-addressable main memory. Specify the bit fields indicated in the shaded regions for each unspecified signal.

The ISA for Processor B supports LDB, LDW, STB, and STW instructions, but does not support unaligned accesses. Note the additional control signal DS (data size), where 1 designates word access, and 0 designates byte access. Write the logic equations for  $CE_0$ ,  $WE_0$ , ...,  $CE_3$ ,  $WE_3$  in terms of the inputs shown. Do not use more inputs than required to specify each output.

$$CE_{0} = ME \cdot A[1]$$

$$CE_{1} = ME \cdot A[1]$$

$$CE_{2} = ME \cdot A[1]$$

$$CE_{3} = ME \cdot A[1]$$

$$WE_{0} = \omega \cdot (DS + DS \cdot A[0]) = \omega (DS + A[0]) \quad \text{or} \quad \omega \cdot A[0]$$

$$WE_{1} = \omega \cdot (DS + DS \cdot A[0]) = \omega (DS + A[0]) \quad \text{or} \quad \omega \cdot A[0]$$

$$WE_{2} = \omega \cdot (DS + DS \cdot A[0]) = \omega (DS + A[0]) \quad \text{or} \quad \omega \cdot A[0]$$

$$WE_{3} = \omega \cdot (DS + DS \cdot A[0]) = \omega (DS + A[0])$$

$$WE_{3} = \omega \cdot (DS + DS \cdot A[0]) = \omega (DS + A[0])$$

| Name: |      |  |

|-------|------|--|

|       | <br> |  |

## Problem 3 (20 points):

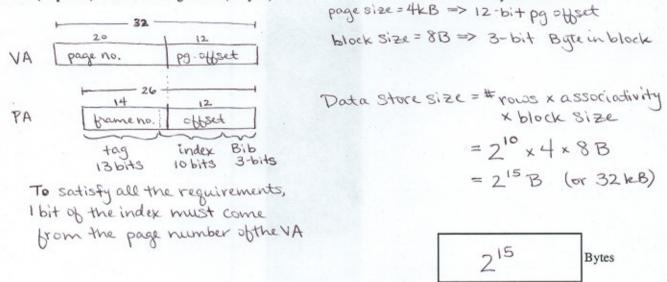

A physically addressed cache is one in which the physical memory locations of each cache line can be inferred from its tag store information.

We want to design a physically addressed, 4-way set-associative, write back cache with a random replacement policy. Line size is 8 bytes. Virtual memory is byte-addressable, with a 32-bit address space, and the page size is 4kB. Physical memory has a 26-bit address space. The memory management system restricts even numbered virtual pages to even numbered physical frames and odd numbered virtual pages to odd numbered physical frames.

We want to be able to access the TLB, tagstore, and data store of this cache concurrently.

So we do not have to worry about back-translation tables, restrictions on shared frames, or invalidating the cache on a context switch, we insist that a line of physical memory cannot be present in more than one slot in the cache at the same time.

Part a (10 points): What is the largest size (in bytes) of the data store of the cache that will satisfy all of the above?

Part b (10 points): What is the minimum size (in bits) of the corresponding tag store?

| Name: |  |

|-------|--|

|       |  |

|       |  |

## Problem 4 (20 points)

A machine has a two-level virtual address translation mechanism similar to the VAX.

The machine's memory system is defined as follows:

Virtual Memory Size: 4KB

Physical Memory Size: 256 Bytes

Page Size: 32 Bytes

Memory is byte-addressable

Virtual address space is partitioned into P0 space, P1 space, system space and reserved space. The space a virtual address belongs to is specified by the most significant two bits of the virtual address, with 00 indicating P0 space, 01 indicating P1 space, and 10 indicating system space.

A PTE consists of a Valid bit, 3 bits for protection, a Reference bit, a Modified bit, and the Page Frame Number (PFN).

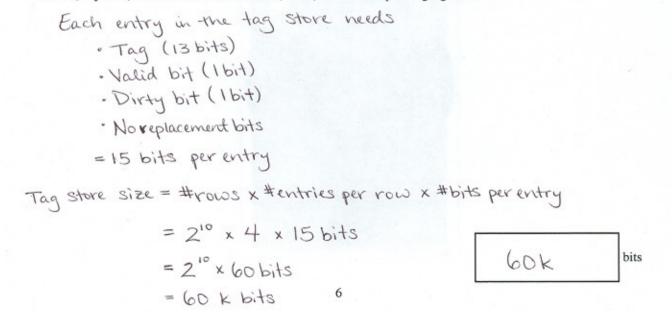

Part a (2 points): What is the minimum size of a PTE in Bytes?

Part b (2 points): Using the PTE size from part a, what is the maximum size of a process' P0 page table in Bytes?

# of pages in PØ space =

$$(\frac{1}{4})(2^{12})$$

(# of bytes in PØ space)

$= 2^5$  pages

Each page of PØ space

needs a PTE in the page

table

page table = #entries x Size of PTE

$= 2^5 \times 2$  Bytes

$= 64$  Bytes

| Name: | 31, |  |

|-------|-----|--|

|       |     |  |

### Problem 4 continued

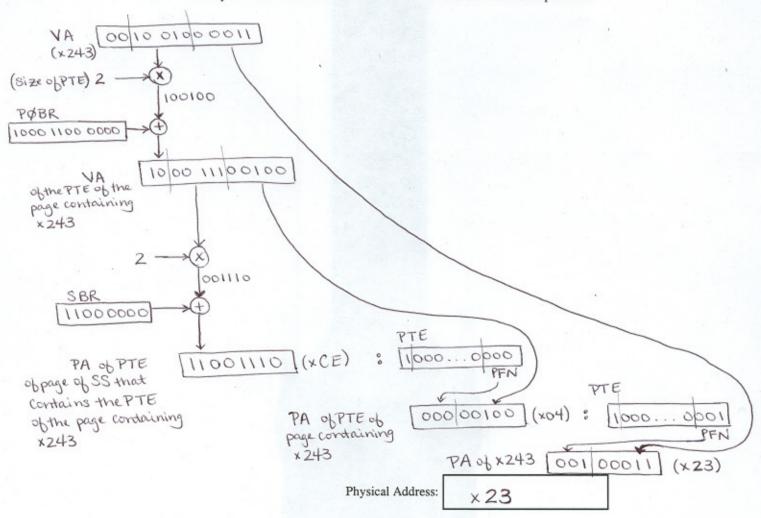

Part c (8 points): If P0BR is x8C0 and the SBR is xC0, what is the physical address corresponding to virtual address x243? Assume that the valid bit of a PTE is its most significant bit and the PFN is stored in its least significant bits.

The following blocks are the contents of a selected areas of physical memory that you may need to solve this problem:

| xCE | x8000 | xE0 | x8004 | x00 | x0002 | x80 | x0438 |

|-----|-------|-----|-------|-----|-------|-----|-------|

| xD0 | x0007 | xE2 | x00A0 | x02 | x8002 | x82 | x0000 |

| xD2 | x8003 | xE4 | x0003 | x04 | x8001 | x84 | x8005 |

| xD4 | x0000 | xE6 | x0007 | x06 | x0134 | x86 | x0002 |

Note: There may be more information contained here than needed to solve the problem.

| Name: |  |  |

|-------|--|--|

|       |  |  |

#### Problem 4 continued

Part d (3 points): Let's say that during the translation of virtual address x243, the valid bit of the 2nd PTE encountered was a 0, resulting in a page fault. What range of virtual addresses in P0 space would also result in this page fault?

The 2nd PTE is the PTE corresponding to the original VA(x243). A PTE maps one page of virtual memory, 30 all VAs on the same page as x243 will also result in a page fault. To find that range, take x243 and make the low 5 bits 0 (for the lower bound) and 1 (for the upper bound).

x243 = 0010010000011 x240 = 001001000000 x25F = 0010010111111

From x240 to x25F

Part e (5 points): Let's say that during the translation of virtual address x243, the valid bit of the 1st PTE encountered was a 0, resulting in a page fault. What range of virtual addresses in PO space would also result in this page fault?

The 1st PTE is the PTE corresponding to the VA that points to the PO page table, which resides in System Space. This entry being invalid means that an entire page of the PO page table is not in physical memory. Since I page is 32B and each PTE is 2B, I page contains 16 PTEs and therefore, maps 16 pages of PO space. Any VA in these 16 pages would cause a page fault.

Since 16 pages = 512B = 2°B, the lower bound of the range will be x243 with the low 9 bits all 0, and the upper bound will be x243 with the low 9 bits all 1.

x243 = 0010 0100 0011 x200 = 0010 0000 0000 x3FF = 0011111111111

From x 200 to x 3FF

| Name: |  |

|-------|--|

|       |  |

### Problem 5 (20 points):

We wish to use the unused opcode 1010 to implement a new instruction FETCH&OP, which loads a word from memory, performs an operation (OP) on it, and stores the result back to the same memory location. The original value which was loaded from memory is saved in R7, and the condition codes are set based on that value. OP can be ADD, AND, or XOR. The second operand can be either the contents of a register or an immediate value. The specification of this instruction is as follows:

### **Assembler Formats**

FETCH&ADD SR1, SR2 FETCH&ADD SR1, imm5

FETCH&AND SR1, SR2 FETCH&AND SR1, imm5

FETCH&XOR SR1, SR2 FETCH&XOR SR1, imm5

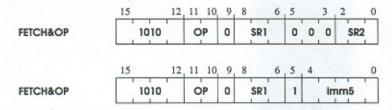

### Encodings

Encoding of the 2-bit value OP is as follows:

ADD/00

AND/01

XOR/10

The value 11 is reserved

#### Operation

| Name: |  |  |

|-------|--|--|

|       |  |  |

#### Problem 5 continued:

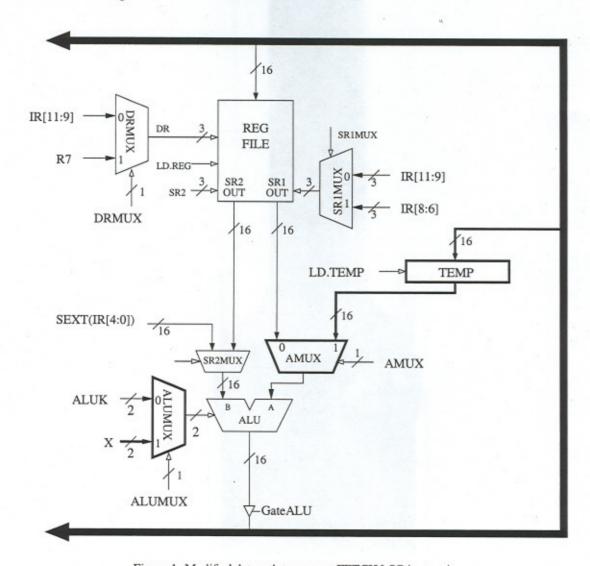

To implement FETCH&OP, we have added the following structures to the LC-3b data path:

1. A 16-bit register called TEMP

This requires a new control field, LD.TEMP, which is the load enable signal for the TEMP register.

2. A two-input mux, AMUX, to the A input of the ALU.

This requires a new control field, AMUX, specified as follows:

SR1/0, the SR1 source from the register file

TEMP/1, the value of the TEMP register

3. A two-input mux, ALUMUX, to the control input of the ALU.

This requires a new control field, ALUMUX, specified as follows:

ALUK/0, the ALUK bits from the control store

X/1, the 2-bit signal X

Figure 1: Modified datapath to support FETCH&OP instruction

| Name: |  |  |  |

|-------|--|--|--|

|       |  |  |  |

### Problem 5 continued:

Part a (2 points): Identify the 2-bit signal X shown on the data path diagram:

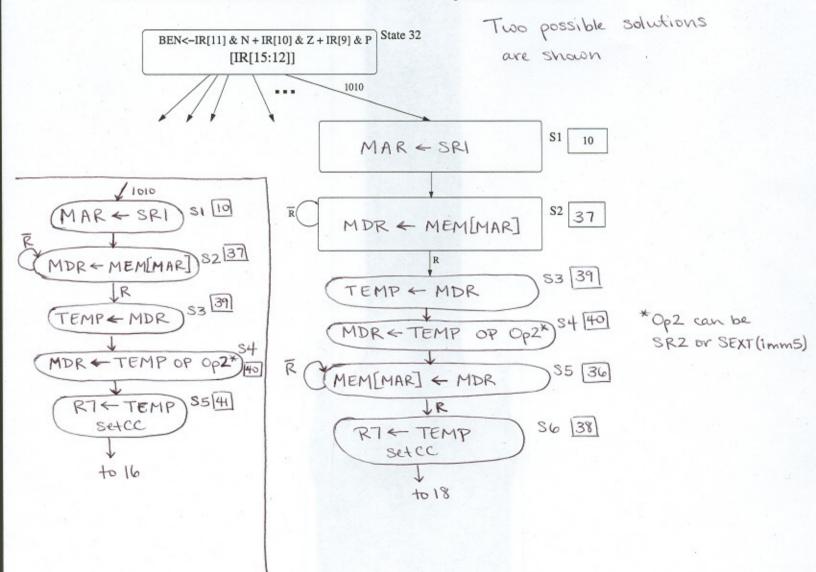

Part b (10 points): We show the beginning of the state diagram necessary to implement FETCH&OP. Using the notation of the LC-3b State Diagram, add the bubbles you need to implement the FETCH&OP instruction. Your job is to describe inside each bubble what happens in each state and assign each state an appropriate state number. You should be able to implement this state diagram using 5 or 6 new states.

NOTE: Your solution must work for instructions where SR2 is R7 e.g. FETCH&ADD R1, R7

| Name: |  |  |

|-------|--|--|

|       |  |  |

#### Problem 5 continued:

Part c (8 points): The processing in each state you just added is controlled by asserting or negating each control signal. Enter a 1 or a 0 as appropriate for the microinstructions corresponding to the states you have added.

NOTE: Please use the encodings specified on the next page for all the signals.

|    | LD.REG | D.Cc | LD.TEMP | LDMAR | LD.MDR | AMUR | SRIMUX | DRMUX | ALIN. | 10:11:01 | ALUMUX | GateALU | GateMDR | MO.EN | R.W. | DATA.SIZE |

|----|--------|------|---------|-------|--------|------|--------|-------|-------|----------|--------|---------|---------|-------|------|-----------|

| S1 | 0      | 0    | 0       | 1     | 0      | 0    | 1      | 0     | 1     | ١        | 0      | 1       | 0       | 0     | 0    | 0         |

| S2 | 0      | 0    | 0       | 0     | 1      | 0    | 0      | 0     | 0     | 0        | 0      | 0       | 0       | - 1   | 0    | 1         |

| S3 | 0      | 0    | ١       | 0     | 0      | 0    | 0      | 0     | 0     | 0        | 0      | 0       | 1       | 0     | 0    | 1         |

| S4 | 0      | 0    | 0       | 0     | À      | ١    | 0      | 0     | 0     | 0        | 1      | ١       | 0       | 0     | 0    | 0         |

| S5 | 0      | 0    | 0       | 0     | 0      | 0    | 0      | 0     | 0     | 0        | 0      | 0       | 0       | 1     | 1.   | 1         |

| S6 | 1      | ١    | 0       | 0     | 0      | ١    | 0      | 1     | 1     | ١        | 0      | 1       | 0       | 0     | 0    | 0         |

These control signals correspond to the 6 state solution on the previous page.